# EVIL FICHT

## **SPANISH MANUAL**

© 1980 Playmatic

#### NORMAS GENERALES DE REPARACION

El sistema modular con que ha sido proyectada y fabricada esta méquine, permite realelizar con un mínimo de tiempo, la reparación por sustitución de los módulos defectuosos, para su posterior reparación en el taller, es decir que en el lugar donde se halla instalada la méquina si la averia es de tipo electrónico, basta con sustituir el módulo defectuoso, para que la máquina quede ce nuevo en funcionamiento en un brevisimo tiempo. A tal fin, los módulos son de reducido tamaño para facilitar tanto las reparaciones debido a sus pocos componentes integrantes, como su transporte. Para ello, se han confeccionado unos estuches que contienen un juego completo de cada módulo así como lo necesario para su sustitución.

Para saber cual de los módulos hay que sustituir, siganse estas

COMO PRECAUCION SUPLEMENTARIA RECOMENDAMOS DESCONECTAR LA MAQUI-NA DE LA RED ANTES DE MANIPULAR LAS TARJETAS, TANTO EN SU DES -CONEXION COMO CONEXION DE LAS MISMAS AL BUS.

- 1).- No se ilumina ningún display, ninguna luz de juego, no fun-

- . Sustituir por este orden hasta encontrar el módulo averiado: PSU (comprobar los fusibles), MPU, IOS.

- 2) -- No se iluminan ningún display pero se enciende fija alguna

- .... Sustituir por este orden hasta encontrar el módulo averiado: PSU (comprobar los fusibles), MPU, IOS.

- 3) -- No se enciende ningún display, pero se encienden las luces de juego, alternando entre ellas.

- .. Sustituir por este orden hasta encontrar el módulo averiado:

4).- Se ilumina el display de algún o algunos jugadores, cambiando de 000.000 = 999.999, pero no todos. .... Sustituir por este orden hasts encontrar el módulo averiado:

- DPY jugedor 10, DPY jugedor 20, DPY jugedor 30, DPY jugedor

- 5) .- Palla el sonido.

.... Sustituir por este orden haste encontrer el módulo averiado:

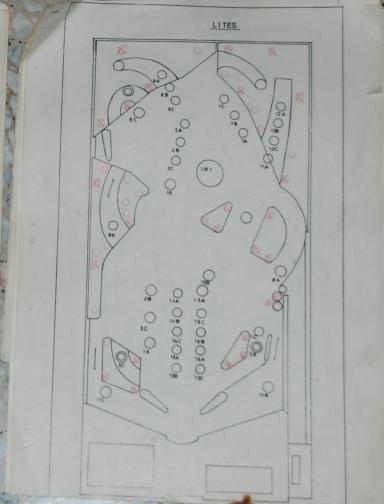

- 6).- Alguns de las luces del juego no se enciende nuncs.

- .... Sustituir por esta orden hasta encontrar el módulo averiado: P. LUCES, LAMPARITA, BLC correspondiente (ver numeración de lemparitas o bien cambiar los tres BLC). Nótese que las luces de bumper llevan un rectificador en el

- 7).- Alguna lamparita de juego, distinta de GAME OVER & HIGH SCO-RE, está encendida siempre.

- .... Sustituir por este orden heste encontrar el módulo averiado: BLC correspondiente (ver númeracion de lamparitae o bien cembier los tres BLC, sucesivamente.

- 8).- No funcionan bumpers, flippers, expulsores, saca bolas, taca,

- .... Sustituir por este orden hasta encontrar el módulo averiado: COMPROBAR SI SE CIEHRA EL RELE CORRESPONDIENTE, SI NO LO HACE

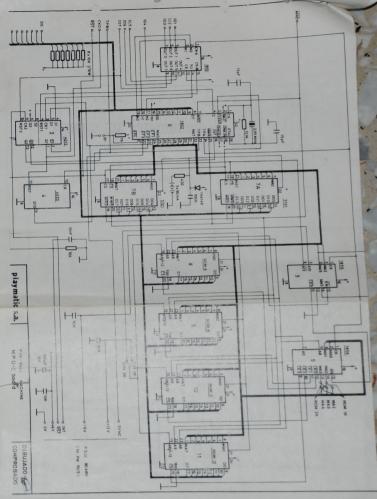

#### DESCRIPCION DE LA TARJETA MPU.

En esta tarjeta se halla situado el conjunto MICROPROCESADOR que consta de:

CPU (6) COSMAC CDP1802.

MEMORIA RAM (7A) y (7B) 5101.

MEMORIA ROM (8), (9), (10) y (11).

DECODIFICADORES DE DIRECTOMES DE MEMORIA (3) y (5) 1859.

DECODIFICADOR INPUTS/OUTPUTS (1) 1853.

FLIP-FLOP DOBLE (2) 4013.

CONTADOR TIMER (4) 4020.

La CPU, controla el funcionamiento de toda la máquina, siguiendo el programa contenido en las memorias ROM. Recibe y envía las señales procedentes o destinadas a los elementos de la máquina a travás de la tarjeta denominaia IOS, a la que está conectada por las conexionas-MRD, IO1, IO2, IO3, IO4, IO5, IO6, IO7, TPB, BUS\$\$\$ DUS\$7. CMD, y RST.

Los DECODIFICADORES (3) y (5), generan las direcciones A8, A9 y A1Ø que no se obtianon diroctamente de la CPU como las AØ-A7, y por medic de las salidas CPØ, CEL, CE2 y CE3, conecton solamente uno de los circuítos de memoria RAM (7) o ROM (8-11) al bus de datos EUSØ-EUS7.

El decodificador (3) al recibir el impulso de TPA, retiene el valor de MA2 y de MA5. Con ollos hace: 1: Si MA5 es positivo hace -CS de las RAM (7) cero seleccionándolas, Si MA5 es negativo hace -CS de las RAM (7) positivo desconectándoles, 2: Si -MRD es positivo hace su salida CEØ positiva por lo que

el decodificador (5) desconectard las ROM. 3: Si MA2 es positivo hace Al¢ positivo. Si MA2 es cero hace Al¢ cero.

El decodificador (5) al recibir TPA retiene el valor de MAØ, MAl y de MA2, MA3 si se usan memorias de HXx8 o MA3, MA4 si se usan momorias de 2Xx8. Con ellos hace: l: Si MAØ, MAI son positivos hace A8, A9 positivos respectivamente y al contrarto.

2: Si la entrada -EN procedente del circuito (3) es positiva todos los CEØ, CEI, CE2, CE3 son positivos y quedan desconectadas las ROM (8-11).

3: Si la entreda -EN es cero, según el valor retenido de MA2, MA3 o MA3, MA4, selecciona una de las ROM haciendo uno de los CEØ a CEØ cero y los demás positivos.

Les MEMORTAS RAM (7A y 7B), son alimentadas permanentemente aún cuando la máquine esta desconectada de la red por modio de una batoría tempón que as recarga sutomaticamente cuando la máquine está contra de Ello tiene por objeto mentener la información almacenada, que de otra forma se perdería. Esta informasión, corresponde a los ajustes de cobro, premio, musicas, juego, etc. y los totalizadores de moncadas, partidas, premios, etc. Estas memorias son desconectadas interiormente cuando su entrada CS (pin 17) es cero. Ello courre cuando catá la red interrumpida. De esta forma se preserva la información que contienen.

La CPU (6), controla las RAM por las direcciones MAØ - MAỹ que indican a que palabra se dirige y por las señales -MRD, -MWR, -CS.

Cuando la CPU desea leer o escribir en las RAM, hace su -CS caro a través del decodificador (3). Si se trata de laer -MRD será cero y -MWR será positivo. Si se trata de escribir -MRD será positivo y -MWR será cero.

Como que cada memoria está organizada en 256 palabras de 4 bit se han colocada dos de ellas con todas las conexiones en paralelo, excepto el bus de datos. En la memoria (7A) se han conoctado BUSØ-BUS3 y en la memoria (7B) se han conectado BUS4-BUS3.

El DECOLFFICADOR I/O (1), genera las señales IOI a IO7 a partir de NØ, N1, N2, TPA, TPB, que son utilizadas para controlar la tarjeta IOS.

El valor de NØ, N1. N2 es retenido desde que recibe el impulso de TPA hasta que recibe el de TPB. Con estas tres señales NØ, N1. N2 decodificadas, se obtienen ocho posibles casos, que corresponden a hacer cero todas las señales IO1 a IO7 o bien a hacer positiva una de ellas, precisamente la que corresponde al circuito de entradas o salidas situado en la tarjeta IOS a la que la CPU quiere conectarse para recibir o suministrar información.

El FLIP-FLOP (2), situado en la parte izquierda del esquema de la tarjeta, gonera la señal de clock que es utilizada para transmitir sincronicamente la información que controla las tarjetas del display a través de un shift register situado en la tarje-

El FLIP-FLOP (2), situado en la parte derecha del esquema de la tarjeta, memeriza la orden de interrupción que se genera en la tarjeta de alimentación FSU, al principio de cada semiciclo de red. La orden es llevade a la CPU por su entrada-INT. Una vez procesada, la CPU envia un impulso por LO7 que borra dicha memorización. (ambos flip-flop están en en mismo circuito integrado (2).

El CONTADOR TIMER (4), genera un impulso cada 2,77 milisegundos que es llevado a la entrada-INT de la CPU a través del flipflop derecho, genera una interrupción para que la CPU refresque la información contenida en el display que va multiplexado.

La señal -RST procedente de la fuente de alimentación PSU, es cero cuando la máquina está desconectada de la red y también inmediatemente después de conectarla durante unas décimas de segundo. En esta situación, desconecta las RAM para preservar su contenido y hace que la CPU inicie la lectura del programa de las ROM por el principio de éste.

La señal SYNC generada en la tarjeta PSU, es positiva durante un semiciclo de la red y coro durante el siguiente y así sucesivamente. Esté conectada a la CPU en -EFJ y es utilizada por esta para sabor si debe activar las lamparitas conectadas en los lo voltios A o bien a las de los lo voltios B.

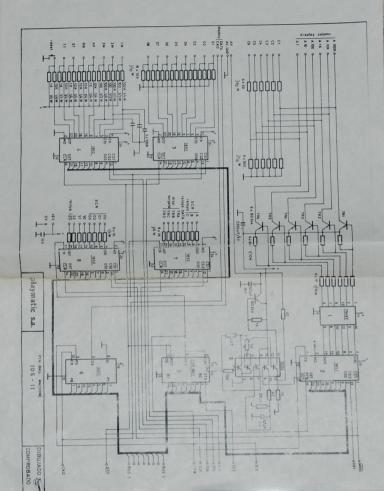

#### DESCRIPCION DE LA TARJETA IOS.

Esta tarjeta enlaza el resto del sistema y la máquina con la tarjeta MPU, que es la que contiene el conjunto microprocesa-

Utiliza los siguientes circuitos:

PUERTAS INPUT/OUTPUT (2), (3), (4), (7) y (8) 1852. DIVISOR PROGRAMABLE (5) CDP1863. 2

- AMPLIFICADORES MULTIPLES (1) 75492 y (9) 3086.

- SHIFT REGISTER (6) 4021.

Los circuitos de las PUERTAS I/O, DIVISOR y SHIFT REGISTER, reciben o envían información a la CPU a través del bus de datos BUSØ a BUS7 cuando la correspondiente línea IOL-IO7 es válida y TPB también lo es.

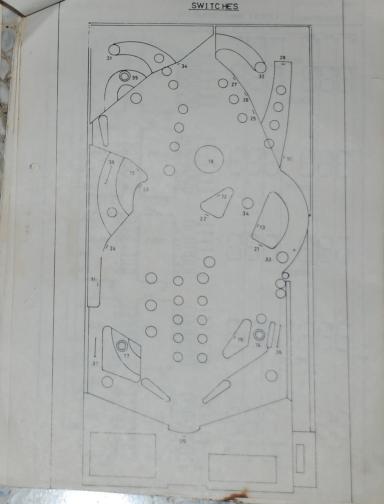

Las puertas (3) y (4), son utilizadas como puertas de entrada. A ellas llegan las conexiones de todos los pulsadores y contactos de la máquina. En la puerta (3), están conectados los con-tactos del tablero de juego en forma de matriz, Cl a C6 por un lado y 01 a 08 por el otro lado. En la puerta (4), están conectados los pulsadores del mueble y el de puesta a cero de los totalizadores que está ubicado en esta misma tarjeta. Las entradas procedentes de los micros de los selectores de monedas 1M, 2M y 3M, tienen colocadas unas redes de retardo formadas por una resistencia y un condensador, cuya misión es la de impedir que los impulsos demasiado cortos, (los que se producen al golpear violentamente la puerta) lleguen a la entrada de la puerta (4).

Les puertas (7) y (8), son utilizadas como puertas de salida. A ellas están conectadas las tarjetas que controlan las luces, relés, etc.

La puerta (2), conectada como puerta de salida, envía al display la información que controla los énodos de los dígitos multiplexados a través de los amplificadores del circuito (1) y de los transistores TR1 a TR6. Del colector de dichos transistores se Ceriva por medio de resistencias la información que controla las columnas de la matriz de entradas C1 a C6.

El DIVISOR PROGRAMABLE (5), divide la oscilación procedente de la CPU por la línea TPB, por un valor programable desde la CPU. En la salida denominada OUT, se encuentra la onda cuadrada resultante que es aplicada al amplificador de ganancia variable constituido por el circuito (9) y componentes asociados. La ga-nancia de este amplificador es controlada por la salida DO7 de la puerta (2) y por el potenciómetro. Un transistor de potencia BD244 suministra la amplificación necesaria para atacar el alta-

El condensador conectado en el pin 6 del circuito (9) es cargado por un transistor interior de este circuito si DO7 del circuito (2) es positivo. Al hacerse D07 cero, dicho condensador se descarga lentamente a través de la resistencia en paralelo con él. La tensión de dicho condensador se aplica a través de otro transistor interno del circuito (9) y del potenciómetro de volumen del amplificador. Al descargarse disminuye por consiguiente el volumen obteniendo el efecto "fadding" del sonido.

El SHIFT REGISTER (6), recibe la información en paralelo procedente de la CPU por BUSØ-BUS7 cuando IO2 es válido y la transmite en serie a las tarjetas del display sincronicamente por medio del clock CKD.

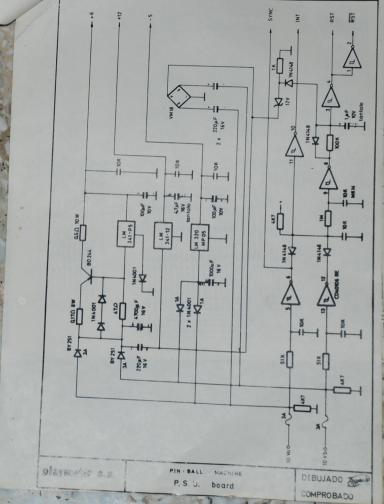

#### DESCRIPCION DE LA TARJETA PSU. (ALIMENTACION)

La fuente de alimentación, suministra las tensiones necesarias para el funcionamiento electrónico de la máquina.

Las tensiones que proporciona son: +6, +12, -5 voltios y en esta misma tarjeta se generan las señales de RST, -RST, INTR y SYNC.

La tensión de 6 voltios, es obtenida a partir de ur rectificador doble onda formado por dos diodos de 3 amperios (BY251), condensador de filtro, transistor de potencia (BD244), es abilizador monolítico (LM341-6) y resistencias de potencia que con los diodos, protegen al transistor de potencia en caso de sobrecarga.

La tensión de 12 voltios, es obtenida a partir de un rectificador/doblador formado por un puente de cuatro diodos monolítico (VMA8) y tres condensadores, este circuito logra una tensión de 15 a 27 voltios (según la tensión del primario), que posterior mente es reducida y estabilizada por medio de un estabilizador monolítico de 0,5 amperios (LM341-12).

La tensión de -5 voltios, es obtenida a partir de un rectificador doble onda formado por dos diodos de l amperio (1N4001)

La señal de INTR, se deriva de las dos tensiones opuestas de alimentación, de forma que se obtenga un impulso cuyo flanco positivo está al principio de cada semiciclo de la red. Esta señal, servirá para sincronizar el disparo de los tiristores que controlan las luces de juego, con el principio del semiciclo de la tensión de red. Estos mismos impulsos, son llevados a una red RC que los integra, de forma que su salida será positiva si falta un solo semiciclo de la red en alguna de ambas entradas de ll voltios A y B procedentes del transformador. Amplificada e invertida por una puerta lógica, esta señal se utiliza para cargar, lentamente a través de una resistencia y descargar rapidamente a través de un diodo, un condensador electrolítico. Es nuevamente amplificada por dos puertas inversoras. De la salida de la primera de las cuales se obtiene RST y de la salida de la segunda -RST. Al conectar la máquina a la red, son RST = 6 voltios y -RST = 0 voltios. Al cabo de 0,1 segundos, cuando se ha cargado ya el condensador son RST = 0 voltios y -RST = 6 voltios. Ambas señales se utilizan para inicializar el sistema electróni-

La señal SYNC es una de las entradas sencidales de los 11 voltios A y B del transformador, convertida en onda cuadrada por medio de una puerta lógica. Se utiliza esta señal en la MPU., para determinar si deben iluminarse las luces de juego conectadas a los 11 voltios A, o a los 11 voltios A.

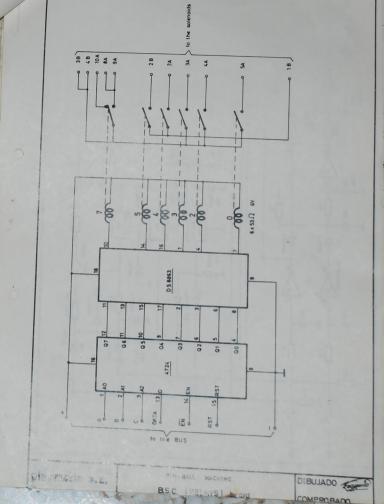

#### DESCRIPCION DE LA TARJETA BSC. (RELES)

Esta tarjeta cuya misión es la de hacer actuar los diferentes electroimanes de la máquina: saca bolas, taca, etc., está equipada con un "8 bit addressable latch" (4724), un driver de ocho vías (DS8863) y hasta 8 relés. (según modelo de máquina)

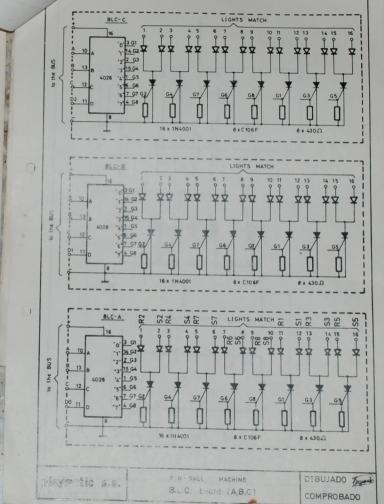

Las seis entradas procedentes de la tarjeta IOS, son: RS cuya misión es abrir todos los relés; tres denominadas A, B, C, que corresvonden a la dirección del relé; una denominada DATA que será voltios si el relé determinado por A, B, C, debe cerrarse o ción -EN indica a este latch cuando la información de las entradas A, B, C, y DATA es estable y válida para ser pasada a memorizeción DESCRIPCION DE LA TARJETA BLC. (CONTROL DE LUCES)

Esta tarjeta, que en número de tres equipa esta máquina, tiene por misión gobernar las luces de juego, o sea las que según las incidencias del juego se van iluminando o apagango.

Su misión es controlar hasta dieciseis grupos de lamparitas distintos.

Se compone de un decodificador 4028, ocho tiristores 17159 (Cio6F) ocho resistencias y dieciseis diodos rectificadores. <sup>C</sup>ada tiristor, puede controlar dos grupos de lamparitas que son alimentadas desde el transformador con dos semiciclos opuestos de tensión alterna.

Las entradas de control DØ, D1, D2, D3 y A, B, C, proceden de la salida del circuito (8) y de la tarjeta IOS respectivamente.

Las entradas A, B, C, se encargan de determinar la dirección o sea cual de las ocho salidas debe ser conectada. La cuarta entrada DØ a D3 es positiva si dicha dirección no debe ser conectada y negativa si debe serlo.

El impulso aplicado a la puerta de los tiristores es de muy corta duración, del orden de los 20 microsegundos pero sufuciente para activar los tiristores, que una vez cebados ya no se desconectarán hasta el final del semiciclo correspondiente. Estos impulsos se repiten en cada semiciclo mientras tenga que estar encendida la lamparita correspondiente.

-12-

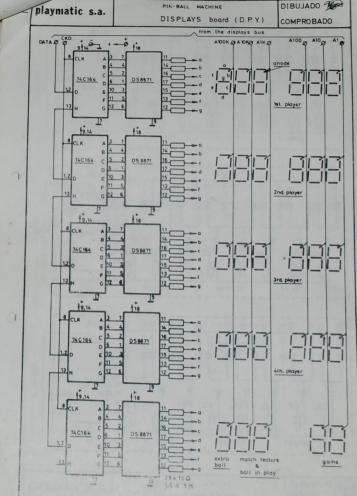

### DESCRIPCION DE LA TARJETA DPY. (DISPLAY)

La tarjeta de display, se compone de un C.T. shift-register de 8 bit (740164), un driver de oche etapas (DS8871), siete resistencies limitadoras y seia dígitos (HDSP3400) de siete segmentos

En la máquina, las cinco tarjetas DPY, están enlazadas en conexión multiplexada, de forma que son comunes los 5 ánodos de los dígitos de 100.000 puntos, los 5 ánodos de los dígitos de 10.000 puntos, etc. formando columnas. Cada una de estas columnas, es alimentada desde la placa IOS., independientemante de las demás y secuencialmente, de forma que unicamente uno de los seis dígitos de cada tarjeta, está iluminado en un instante dado. Como que este proceso se realiza a una velocidad de 50 veces por segundo, el ojo del observador crea la ilusión optica de que están iluminados todos los dígitos simultáneamente. Previamente a la conexión de los ánodos de cada columna, son elegidos los catodos de los segmentos de cada dígito que deben de iluminarse para formar el número deseado.

Un shift-register como los utilizados, al recibir un impulso por su entrada CK, situa en la salida A la información que había en la entrada DATA. Simultaneamente la que había en A pasa a B, la que había en B pasa a C, la que había en C pasa a D, etc.

Desde la tarjeta IOS., se alimentan en paralelo las cinco entradas CK de las cinco tarjetas de display, y la entrada DATA del display del 1º JUGADOR. La salida H de este display, esta conectada a la entrada DATA del display del 2º JUGADOR y así sucesivamente hasta el display del STATUS.

Desde la tarjeta IOS., antes de conectar una columna determinada, son enviados 40 impulsos por la conexión CKD que alimenta las entradas CK de los display. Antes de cada impulso, DATA será 6 voltios ó Ø voltios, según deba iluminarse el segmento al cual llegará dicha información. Evidentemente, los 8 primeros impulsos corresponden al display de STATUS, los 9 al 16 al display del 49 JUGADOR, los 17 al 24 al display del 3º JUGADOR, los 25 al 32 al display del 2º JUGADOR y los 33 al 40 al display del 1º JUGADOR.

Una vez seleccionados los segmentos, dichas informaciones amplificadas por los drivers y limitada su intensidad por las resistencias, son llevadas a los cátodos de los led. Los catodos de los segmentos que ocupan la misma posición en los 6 dígitos de cada display, están conectados en paralelo. Naturalmente solo se iluminarán los de los dígitos de la columna que es alimentada en ese instante desde la placa IOS.

Al cebo de unos 3 milisegundos, es desconectada la columna, actualizada la información de los segmentos siguientes y alimentada la columna, y así sucesivamente.

-----

-

-----