# Cromemco<sup>™</sup> SCC SINGLE CARD COMPUTER

INSTRUCTION MANUAL

CROMEMCO, Inc. 280 Bernardo Avenue Mountain View, CA 94043

Part No.023-0050

January 1980

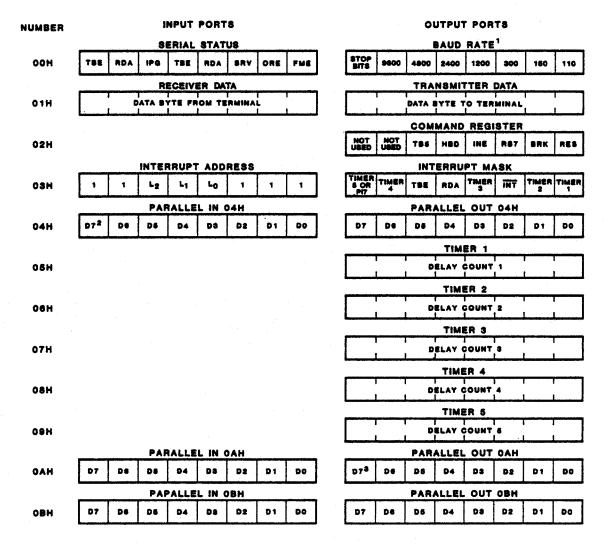

#### SCC I/O PORT SUMMARY

NOTE 1: SETTING PORT OUT 02H BIT HBD TO LOGIC 1 OCTUPLES THESE BAUD RATES.

2: PORT IN 04H BIT D7 MAY BE DEFINED AS AN AUXILIARY INTERRUPT INPUT, REPLACING TIMER 5 AS THE LEVEL 7 INTERRUPT SOURCE, BY SETTING OUT 02H BIT RS7 TO LOGIC 1.

S: PORT OUT OAH BIT D7 CONTROLS SCC MEMORY ENABLE/DISABLE IF THE MEMORY DISABLE FUNCTION IS SELECTED. D7=LOGIC 0 ENABLES SCC MEMORY

# **Cromemco** SCC SINGLE CARD COMPUTER

**INSTRUCTION MANUAL**

CROMEMCO, Inc. 280 Bernardo Avenue Mountain View, CA 94043

Part No.023-0050

January 1980

Copyright © 1979, 1980 By CROMEMCO, inc. ALL RIGHTS RESERVED This manual was produced on a Cromemco System Three computer using the SCREEN Editor. The edited text was formatted using the Cromemco Word Processing System Formatter. Final camera-ready copy was printed on a Cromemco 3355A printer.

### TABLE OF CONTENTS

| Section              | 1:                       | INTRODUCTION 1<br>TECHNICAL SPECIFICATIONS 3                                                                                                                                                                                                                   |

|----------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section              | 2:                       | OPERATING INSTRUCTIONS                                                                                                                                                                                                                                         |

|                      | 2.6<br>2.7<br>2.8<br>2.9 | SCC CENTRAL PROCESSING UNIT5SCC POWER, POWER-UP, RESET6SCC MEMORY ORGANIZATION8SCC MEMORY EXPANSION / DISABLE12SCC PIN-OUTS & INTERFACE CABLING19SCC PARALLEL I/O PORTS22SCC SERIAL I/O27SCC INTERVAL TIMERS43SCC INTERRUPTS51INTERRUPT PROGRAMMING EXAMPLES69 |

| Section              | 3:                       | SYSTEMS CONSIDERATIONS                                                                                                                                                                                                                                         |

|                      | 3.2                      | SCC SYSTEM INITIALIZATION                                                                                                                                                                                                                                      |

| Section              | 4:                       | THEORY OF OPERATION106                                                                                                                                                                                                                                         |

|                      |                          | SCC FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                     |

| Section              | 5:                       | A SIMPLE SCC EXAMPLE SYSTEM124                                                                                                                                                                                                                                 |

| Appendi:<br>Appendi: |                          | SCC I/O PORT SUMMARY136<br>ASCII CHARACTER SET145                                                                                                                                                                                                              |

|                      |                          | SCC PARTS LIST                                                                                                                                                                                                                                                 |

#### Section 1

#### INTRODUCTION

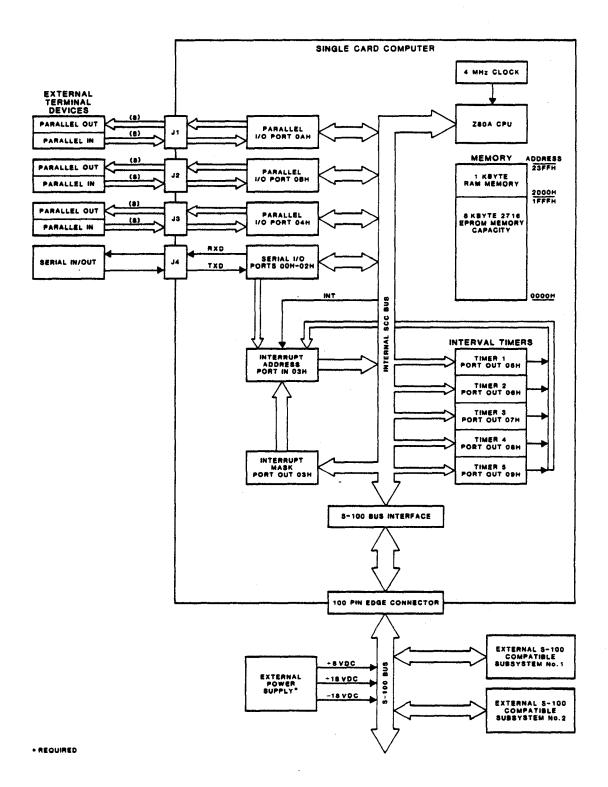

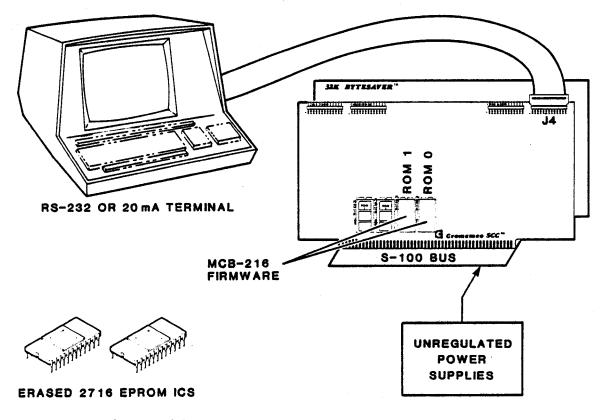

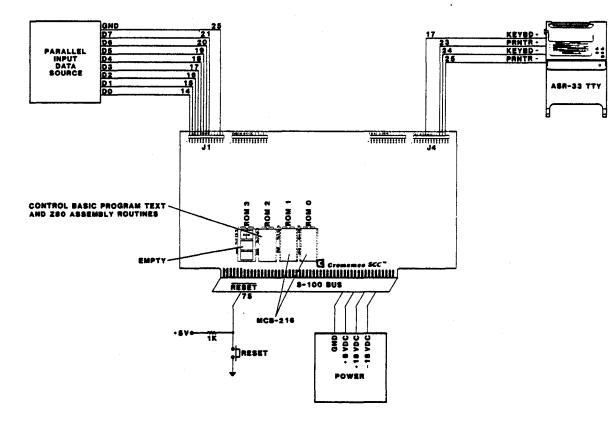

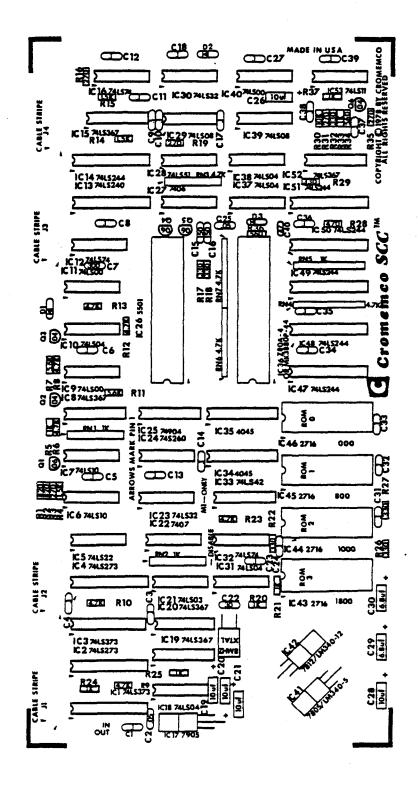

The Cromemco Single Card Computer (SCC) is a Z80A based, S-100 bus microcomputer subsystem. The SCC is self-contained, excepting external power, making it an ideal choice for small to medium-scale dedicated applications. The SCC provides all the features one could want in a powerful, yet reasonably priced, single card microcomputer (see Figure 1):

<u>Processor</u>: The powerful Z80A clocked at 4,000 MHz - with the 8080A instruction set as a subset of its own 158 instruction set.

<u>Memory</u>: 1 Kbyte of 4045 static RAM and space for 8 Kbytes of 2716 EPROM firmware.

Firmware: Cromemco's Z80 Monitor and 3K Control BASIC available on two ROMs (model MCB-216).

Parallel I/O: Three independent 8-bit parallel output ports, and three independent 8-bit parallel input ports, all with handshake.

<u>Serial I/O</u>: One RS-232/20 mA current loop serial I/O port with software selectable baud rate.

<u>Interval Timers</u>: Five independent interval timers with range 0 - 16.32 mSec and resolution 64 uSec generating prioritized interrupts on Count 00.

Interrupts: Supports all three Z80 interrupts modes; one SCC input port contains the highest priority interrupt requesting service; one SCC output port selectively masks-off unwanted interrupt sources.

Expandability: Compatible with all Cromemco S-100 products. Thus, the standard SCC functions may be enhanced by adding Cromemco cards for A/D and D/A conversion, RAM/ROM memory expansion, color graphics, line printer interfacing, floppy disk interfacing, and more.

Figure 1: SCC FUNCTIONAL BLOCK DIAGRAM

#### SCC TECHNICAL SPECIFICATIONS

Z80-A Processor Type: 4.000 MHz Clock Frequency: 158 instructions including the 78 Instruction Set: member 8080A CPU instruction set 8 KBytes spanning address range ROM Capacity: 0000H - 1FFFHROM Type: Intel 2716 EPROM, TI 2516 EPROM, or equivalent (user supplied) 1 KBytes spanning address range RAM Capacity: 2000H - 23FFH 4045 Static (included) RAM Type: UART Type: TMS 5501 or equivalent Serial I/O Port: RS-232 or 20 mA current loop; software selectable from 110 to 76,800 Baud, one or two stop bits Parallel Ports: 24 lines of input data organized as three parallel 8-bit ports; 24 lines of output data organized as three parallel 8-bit ports Interval Timers: 5 independent timers with range 0 -16.32 mSec and 64 uSec resolution All three Z80 interrupt modes Interrupts: supported (IM 0, IM 1 & IM 2); prioritized IM 0 RST vectors may be automatically supplied by eight SCC interrupt sources Cromemco Standard-100 (S-100) Bus Compatibility: Power Requirements: +8 VDC @ 1.75 Amps (max) +18 VDC @ 100 mA (max) -18 VDC @ 50 mA (max) 0 - 55 degrees Celsius Operating Environment:

ABOUT THIS MANUAL:

The remainder of this manual is divided into four major sections: Section 2, <u>Operating Instructions</u>; Section 3, <u>System</u> <u>Considerations</u>; Section 4, <u>Theory of Operation</u>; and Section 5, <u>A</u> <u>Simple SCC Example System</u>.

Section 2 provides detailed descriptions of all SCC subsystems (memory, serial/parallel I/O ports, interval timers, etc.). An adjunct to this section is Appendix A, SCC I/O Port Summary. The reader is encouraged to scan Appendix A before studying Section 2 in detail to get an overview of SCC I/O port functions. Also note the quick-reference SCC I/O Port Summary which appears on the manual overleaf.

Section 3 discusses the SCC in a system context. The various system initialization tasks and options discussed throughout Section 2 are gathered together in this section, together with a discussion of SCC development systems.

Section 4 provides an analysis of the major SCC logic functions and signal paths, and finally Section 5 presents a simple, yet complete and illustrative example system to codify many of the ideas presented earlier in the manual. The experienced user would profit from scanning Section 5 before reading the other manual sections.

#### Section 2

#### **Operating Instructions**

The SCC is a highly versatile control subsystem which must be defined and viewed in its final system context. Consequently, the SCC operating instructions cannot be effectively reduced to a simple step-by-step formulation. Instead, pertinent operating instructions are topically grouped by function in the subsections which follow. The SCC user is urged to read this material in its entirety with the aim of selecting among the SCC options and modes which best meet his own final system requirements.

#### 2.1 SCC CENTRAL PROCESSING UNIT

The heart of the SCC is its Z80A central processing unit (CPU). The Z80A is an 8-bit processor which can directly address 64 KBytes of memory (locations 0000 thru FFFF hexadecimal), 256 input ports and 256 output ports (ports 00 thru FF hexadecimal). The Z80's 158-member instruction set includes the 8080's 78-member instruction set as a subset. Moreover, the Z80 supplies extended capabilities such as bit test, block search/move, relative jumps, a complete alternate register set, two index registers, three interrupt modes, a non-maskable interrupt input pin, and more, which the 8080 does not. Please refer to the Z80 Technical Manual for full details.

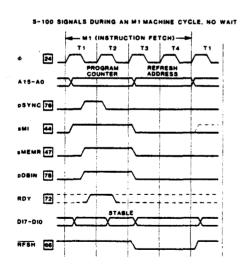

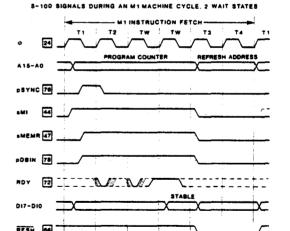

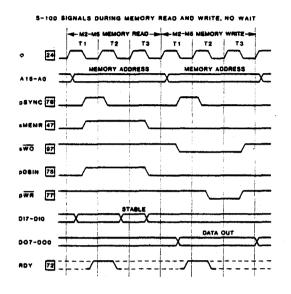

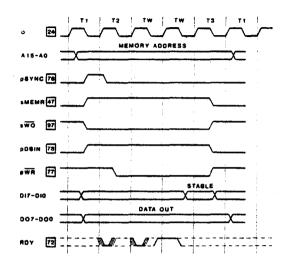

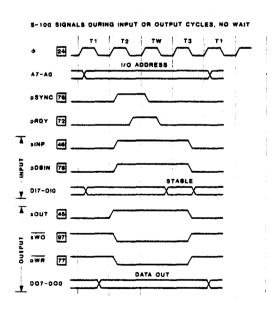

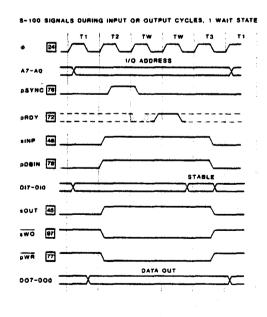

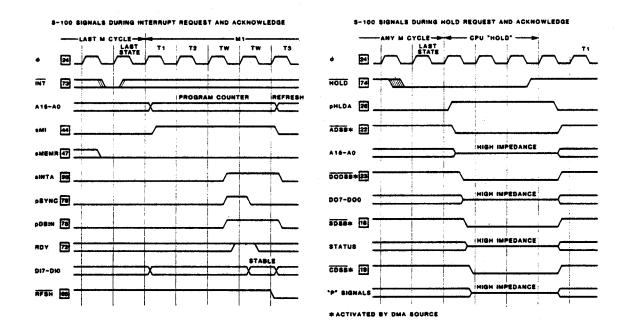

The Z80A is clocked at a fixed 4.000 MHz on the SCC yielding a 250 nSec CPU cycle time. Thus Z80A instruction execution time

ranges from 1.00 uSec (for 4-cycle instructions) to 5.75 uSec (for 23-cycle instructions) with no wait states. Instruction execution time may be extended an indefinite integral number of idling CPU cycles, or 'wait states', by asserting S-100 bus line RDY low to synchronize the CPU to slow memory or I/O.

Z80A support hardware on the SCC generates an ensemble of S-100 bus status and processor control signals making the SCC fully compatible with all Cromemco S-100 products. These include additional RAM memory (4KZ RAM Card, 16KZ RAM Card, 64KZ RAM Card), EPROM memory and programmer cards (Bytesaver II, 32K Bytesaver), parallel I/O cards (8PIO, Isolated 4PIO), an A/D and D/A card (D+7A), a serial interface card (TU-ART), a floppy disk controller card (4FDC), color graphics interface cards, and a line printer interface card (PRI).

#### 2.2 SCC POWER, POWER-UP, RESET

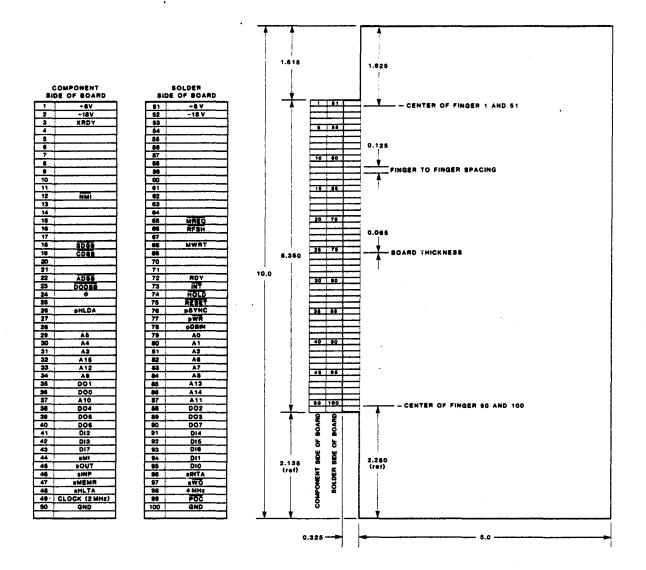

The SCC card requires three unregulated power supply voltages: +8 VDC @ 1.75 Amps (S-100 pins 1 and 51); +18 VDC @ 100 mAmps (pin 2); and -18 VDC @ 50 mAmps (pin 52). Voltage regulators on the SCC itself regulate these voltages to +5 VDC, +12 VDC and -5 VDC respectively.

Applying power (+8 VDC) causes SCC circuitry to automatically generate a momentary low level Power-On Clear pulse on S-100 bus line POC, which in turn resets the Z80A, clears SCC parallel ports OUT 0AH and OUT 0BH, unconditionally enables the SCC on-board

memory, and resets any other devices which respond to an active low level on S-100 bus line RESET. The Z80A responds to an active low level on its RESET pin by (1) Disabling Interrupts, (2) Resetting its I (IM 2 Interrupt Address) Register to 00H, (3) Resetting its R (Refresh Address) Register to 00H, (4) Setting Interrupt Mode 0 (IM 0), and finally, (5) Performing a Jump to memory location 0000H. The SCC provides 8 KBytes of contiguous 2716 EPROM memory space starting at 0000H, thus the SCC user would typically locate a system initialization routine in 2716 EPROM starting at location 0000H, or alternately use the Cromemco MCB-216 ROM chip set which has provisions for either automatically running user defined 3K Control BASIC firmware, or entering the interactive 3K Control Basic command mode.

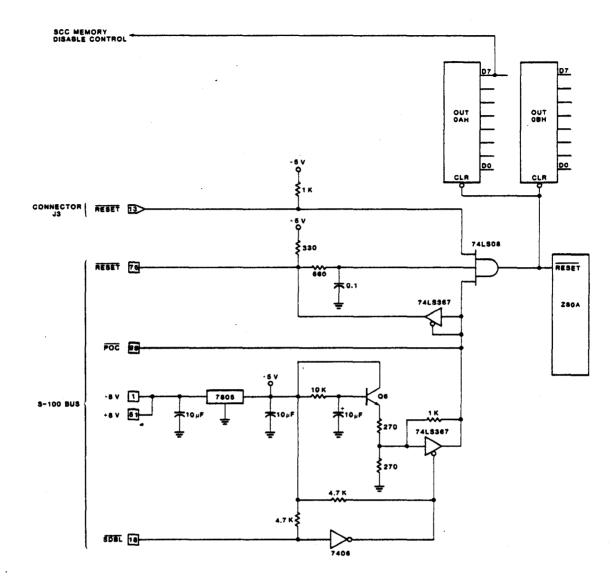

In addition to a POC, there are two other sources which may generate an SCC system reset. The first is from S-100 bus line RESET which again resets the Z80A, clears SCC parallel ports OUT OAH and OUT OBH, unconditionally enables SCC on-board memory, and effects any other S-100 bus cards which are connected to the RESET line. The second source is from SCC connector J3 (one of the four 25-pin connectors provided along the top edge of the SCC card), pin 13. This line is also labeled RESET, and an active low level on this line causes the same SCC response as described above, but it does not force S-100 bus line RESET active low. This second method provides a means for an external device to reset the SCC subsystem, and not effect other S-100 cards in the process. Figure 2 illustrates these three reset sources.

Figure 2: SCC RESET SOURCES

#### 2.3 SCC MEMORY ORGANIZATION

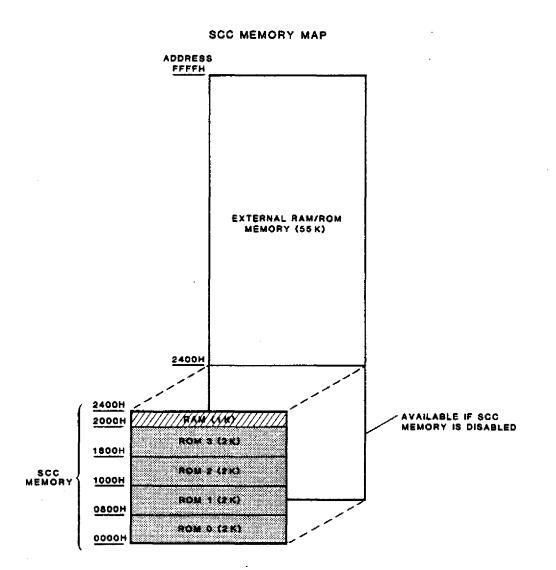

The SCC provides space for 8 KBytes of 2716 EPROM memory in sockets ROM 0, ROM 1, ROM 2 and ROM 3, spanning addresses 0000H thru 1FFFH in 800H increments (2 KBytes), and 1 KByte of 4045 static RAM memory spanning 2000H thru 23FFH. The SCC memory map is shown in Figure 3.

The Intel 2716 (or TI 2516) is a 2 K by 8-bit Erasable Programmable Read Only Memory (EPROM) with a 450 nSec (max) memory (Note that Texas Instrument's 2716 EPROM is not access time. equivalent to the Intel 2716, and thus may not be used in the The device is typically shipped from the manufacturer in SCC.) the 'erased' condition (all bits set to logic 1), and is programmed by selectively resetting individual bits to the logic 0 state using a 2716 programming device such as Cromemco's 32K Bytesaver card. Once programmed, the 2716 retains the programmed bit pattern until re-programmed (in which case logic 1 bits may be re-programmed to logic 0 bits, but not vice versa), or until the entire device is erased by exposure to ultra-violet light which un-selectively returns all array bits to the logic 1 state (see manufacturer's specifications for detailed EPROM erasure procedures).

All, none, or any combination of SCC ROM sockets may be populated by user-supplied 2716 EPROMs. Performing a memory read on an empty SCC ROM socket almost always reads data OFFH (all bits logic 1 from floating data lines); performing a memory write to an empty SCC ROM socket has no effect other than consuming time, but writing to a full socket <u>should be avoided</u> as there will be a data bus conflict between the Z80A write data and the 2716 read data.

Figure 3: SCC MEMORY MAP

Since the 2716 has a memory access time of 450 nSec while the CPU cycle time is 250 nSec, the SCC automatically inserts one wait state during all memory request machine cycles to the lowest 8 KBytes of memory (0000H - 1FFFH) where 2716 EPROM memory resides. Note that these wait states will not be inserted if the SCC memory

is disabled and external user-supplied memory occupies the 0000H lFFFH area (see Section 2.4).

The number of required wait states versus memory access time, assuming the SCC Z80A processor with its 4.000 MHz symmetric clock, are tabulated below:

#### TABLE 1: WAIT STATES

| WAIT STATES | MEMORY ACCESS TIME |

|-------------|--------------------|

| REQUIRED    | (NANOSECONDS)      |

| NONE                   | 340 (MAX) |

|------------------------|-----------|

| ONE EACH M1 CYCLE ONLY | 455 (MAX) |

| ONE PER MEMORY CYCLE   | 590 (MAX) |

The SCC provides a jumper option which is labeled 'M1 ONLY' on the board legend (see Figure 4), and 'INSERT JUMPER FOR M1 WAITS ONLY' on the SCC Schematic Diagram. Installing an insulated jumper wire connecting the open-circuited M1 ONLY soldering pads will cause one wait state to be inserted only during M1 fetch cycles to the lowest 8 KBytes of memory. Note that even though the 2716 satisfies the 455 nSec (max) memory access requirement for M1 WAITS ONLY, it only marginally does so. Thus the SCC is shipped from Cromemco with the option de-selected. The option is included primarily to anticipate faster versions of the 2716.

Figure 4: M1 WAITS JUMPER OPTION

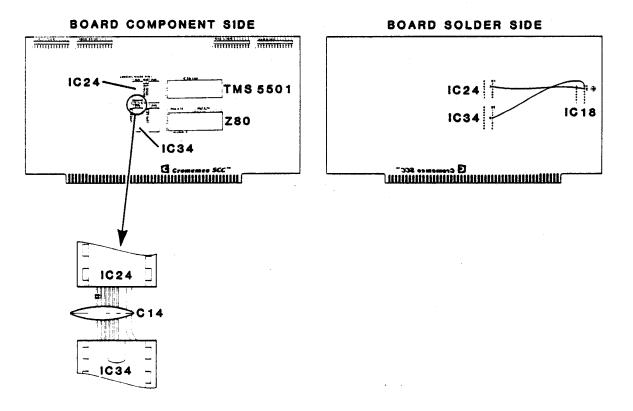

The SCC read/write memory physically consists of two 4045 1 K by 4-bit static RAMs occupying sockets IC34 and IC35. Since the 4045 memory access time is 250 nSec (max), no wait states are required for these devices. IC35 contains the high-order nybble of each RAM byte, and IC34 contains all low-order nybbles. When power is first applied to the SCC, the RAM contents should be assumed random.

#### 2.4 MEMORY EXPANSION/SCC MEMORY DISABLE

The amount of memory available to the SCC may be expanded by merely plugging additional RAM or ROM memory cards into the SCC controlled S-100 bus. The additional S-100 bus compatible memory

may overlap, be disjoint with, or be contiguous with the SCC onboard memory. It is the external memory's responsibility to insert wait states by controlling S-100 bus line RDY, if necessary, for 4 MHz operation.

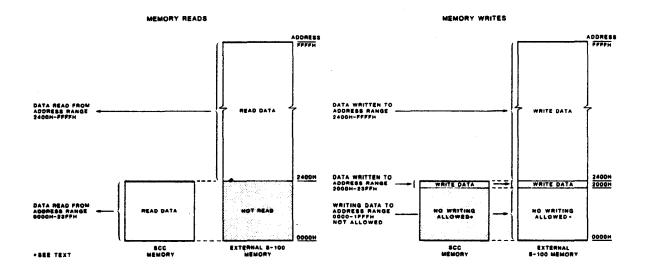

Installing external memory which overlaps the SCC 0000H -23FFH memory area gives rise to the situation illustrated in Figure 5. For memory reads, the SCC reads data only from its onboard memory in the address range 0000H - 23FFH, and from the external S-100 bus in the address range 2400H - FFFFH; any external memory residing in the 0000H - 23FPH area is simply ignored. For memory writes, the SCC writes data to its on-board memory and to the external S-100 bus in <u>parallel</u>, although writing to the SCC ROM area 0000H - 1FFFH does not alter the 2716 EPROM contents. Stated another way, the SCC 'listens' to only its own memory when the memory address is in the range 0000H - 23FFH, and on-board RAM memory is 'transparent' to all memory write operations (empty on-board ROM sockets are also transparent to memory writes).

Figure 5: MEMORY OVERLAPPING THE SCC

Additional memory may be added up to the Z80A's 64 KByte direct addressing limit, and by incorporating Cromemco's memory products with <u>Bank Select</u>, memory may be expanded further to 512 KBytes organized as eight 'banks' of 64 KBytes each. Cromemco memory boards with Bank Select (RAM Boards: 4KZ, 16KZ, 64KZ; EPROM Boards: Bytesaver II, 16KPR, 32K Bytesaver) are mapped into any combination of Memory Banks (Bank 0 thru Bank 7) by setting an eight position slide switch on the card. Banks are enabled and disabled under software control by outputting a bank select control byte to port OUT 40H, an integral output port on each Cromemco product with Bank Select. If a logic 1 bit (D0 thru D7)

in the bank select control byte matches any Memory Bank the board is mapped into, the memory board becomes active and is thus switched 'into' the memory map. Conversely, if there is no match between any bank activated by the control byte and the banks the board is mapped into, the board goes inactive, and thus is switched 'out of' the memory map. Finally note in connection with the Bank Select feature that SCC on-board memory is <u>not</u> Bank Select controlled. An example will illustrate the foregoing ideas.

#### EXAMPLE 1

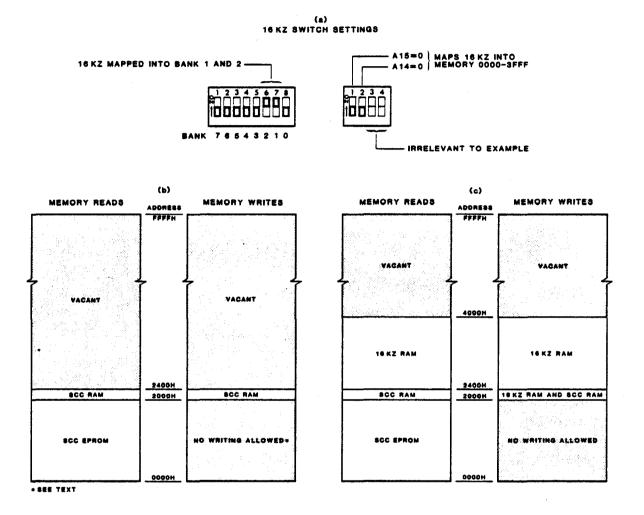

Suppose a 16KZ RAM board, with the switch settings shown in Figure 6A, is co-resident with an SCC in an S-100 bus. The switch settings map the 16KZ into the address range 0000H - 3FFFH (the lowest 16 KBytes of memory) in Memory Banks 1 and 2.

(a) When power is first applied, SCC memory unconditionally enables. The 16KZ responds to a POC by enabling only if it is mapped into Bank 0, and disabling otherwise. Thus, the 16KZ is switched out of the memory map in response to a POC. The system memory map immediately following a POC is shown in Figure 6b.

(b) Now suppose the following two instructions, residing in SCC ROM 0, are executed:

ADDR OBJECT MNEMONIC

COMMENT

| 0000 | 3E82 | LD  | A,10000010B | ; ENABLE | BANK 1 &  | BANK | 7 |

|------|------|-----|-------------|----------|-----------|------|---|

| 0002 | D340 | OUT | 40H,A       | ;OUTPUT  | CONTROL 1 | BYTE |   |

The 16KZ is mapped into one of the banks activated by the bank select control byte (Bank 1), thus it is switched into the memory map (Figure 6C).

(c) Finally assume the following two instructions, also residing in SCC ROM 0, are executed:

| ADDR | OBJECT | MNEMO | NIC         | COMMENT |              |

|------|--------|-------|-------------|---------|--------------|

| 0004 | 3E01   | LD    | A,00000001B | •       | ONLY BANK 0  |

| 0006 | D340   | OUT   | 40H,A       |         | CONTROL BYTE |

Since the 16KZ is not mapped into Bank 0, it is switched out

of the memory map in response to the control byte, and the memory map reverts back to that shown in Figure 6b.

#### Figure 6: EXAMPLE 1 SWITCH SETTING & MEMORY MAPS

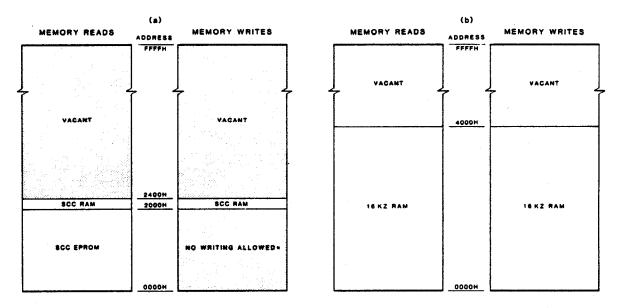

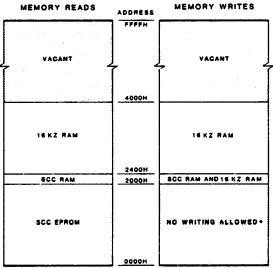

Although the SCC on-board memory does not respond to Bank Select, a functionally equivalent software controlled memory enable/disable option is provided. The <u>Memory Disable</u> option is exercised by cutting the existing foil trace between the two solder pads labeled 'DISABLE' on the SCC board legend (see Figure 7). With the trace cut, high order bit D7 of SCC parallel port

OUT 0AH controls the SCC memory enable/disable function. Setting bit D7 to logic 1 disables SCC memory; resetting bit D7 to logic 0 enables SCC memory. Either a POC or a RESET unconditionally enables the on-board SCC memory, since either a POC or an active low level on S-100 bus line  $\overline{\text{RESET}}$  resets all parallel port OUT 0AH bits to logic 0. If the Memory Disable trace is left in its factory shipped closed condition, or if it is later re-installed, bit D7 of port OUT 0AH has no effect on SCC memory enable/disable.

#### EXAMPLE 2

Assume the same 16KZ RAM and SCC configuration as in Example 1, and also assume the SCC Memory Disable option is selected by cutting the foil trace.

(a) After power is first applied, the 16KZ automatically disables since it is not mapped into Bank 0, and the SCC on-board memory unconditionally enables since all bits of port OUT 0AH are reset to logic 0. The resulting memory map is shown in Figure 7A. Note that an S-100 RESET after power is applied produces the same map.

(b) Now suppose the following four instructions, residing in SCC ROM 0, are executed:

| ADDR                 | OBJECT               | MNEMO           | ONIC .                              | COMMENT                                                                   |

|----------------------|----------------------|-----------------|-------------------------------------|---------------------------------------------------------------------------|

| 0000<br>0002<br>0004 | 3E82<br>D340<br>3E80 | LD<br>OUT<br>LD | A,10000010B<br>40H,A<br>A,10000000B | ;ENABLE BANK 7 & BANK 2<br>;OUTPUT CONTROL BYTE<br>;SET BIT D7 TO LOGIC 1 |

| 0006                 | D30A                 | OUT             | OAH,A                               | ;DISABLE SCC MEMORY                                                       |

The first two instructions activate the 16KZ since it is assumed switch-mapped into Bank 2, and the next two instructions disable all SCC memory by setting bit D7 of port OUT OAH to logic 1 (Figure 7B). Note that after the four instructions above are executed, the Z80A will fetch the next opcode from 16 KZ RAM address 0008H (the next sequential address). Thus provisions must be made to maintain program continuity when bank switching in this fashion.

(c) Finally suppose the following two instructions, residing in SCC ROM 0, are executed:

| ADDR | OBJECT | MNEMO | NIC        | COMMENT                  |  |

|------|--------|-------|------------|--------------------------|--|

| 8000 | 3E00   | LD    | A,0000000B | ;RESET BIT D7 TO LOGIC 0 |  |

| 8000 | D30A   | OUT   | 0Ah,A      | ;ENABLE SCC MEMORY       |  |

Since no Bank Select control word is output, the 16KZ remains in the map. The two instructions above also enable SCC memory (Figure 7c).

(c)

\* SEE TEXT

#### Figure 7: EXAMPLE 2 MEMORY MAPS

-----

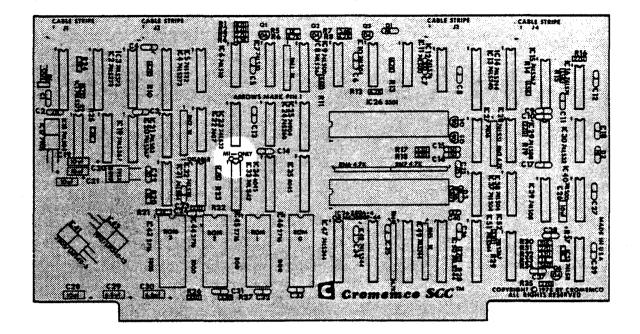

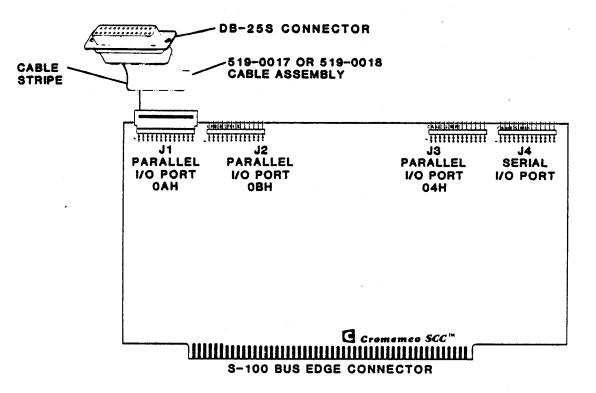

#### 2.5 SCC PIN-OUTS & INTERFACE CABLING

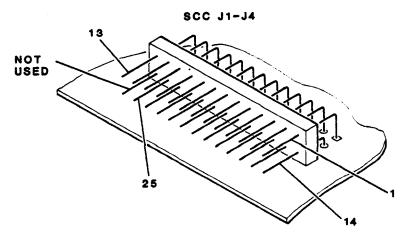

The SCC may communicate with external terminal devices either over the S-100 bus, or thru four SCC connectors J1, J2, J3, and J4 located along the top edge of the board (see Figure 8). The S-100 bus is, of course, a general purpose interface, while connectors J1 - J4 provide the data paths for one serial and three parallel SCC I/O ports. A discussion of the SCC controlled S-100 bus is presented in Section 4.2 of this manual.

Figure 8: SCC CONNECTORS J1, J2, J3 & J4

Cromemco provides two interface cables which are plug compatible with SCC connectors Jl thru J4; Part No. 519-0017 (62 cm, \$15) and Part No. 519-0018 (110 cm, \$15). Each of these cable assemblies consists of a 26-pin female connector which mates with one SCC terminal strip connector J1 - J4, a 25-conductor flat ribbon cable of length 62 or 110 cm, and a 25-pin female DB-25S EIA terminating connector. The terminal devices should be equipped with a mating 25-pin male DB-25P EIA connector when using either of these Cromemco supplied cables.

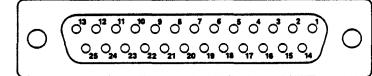

All Jl - J4 pin numbers referenced in this manual and in the SCC Schematic Diagram correspond to the DB-25s EIA pin numbers. Figure 9 illustrates the EIA numbering convention, and also shows the SCC terminal strip numbering convention.

EIA CONNECTOR J1-J4

#### Figure 9: SCC PIN NUMBERING

Cromemco supplied cables must be installed by aligning the board legend arrow head near each connector with the ribbon <u>cable</u> <u>stripe</u> (the colored edge of the ribbon cable). With the cable stripe properly aligned, the pin-outs of SCC connectors J1 thru J4

are shown in Table 2.

#### Table 2

SCC CONNECTOR J1 THRU J4 PIN-OUTS

| Pin                   | Connector Jl      | Connector J2   | Connector J3          | Connector J4 |

|-----------------------|-------------------|----------------|-----------------------|--------------|

| 1                     | NOT USED          | NOT USED       | NOT USED              | NOT USED     |

| 2                     | OUT OAH, DO       |                |                       | TxD          |

| 2<br>3<br>4<br>5<br>6 | OUT OAH, D1       |                |                       |              |

| 4                     | OUT OAH, D2       | OUT OBH, D2    |                       |              |

| 5                     | OUT OAH, D3       | -              |                       |              |

| 6                     | OUT OAH, D4       |                |                       |              |

| 7                     | OUT OAH, D5       |                |                       |              |

| 8<br>9                | OUT OAH, D6       |                |                       |              |

| 9                     | OUT OAH, D7       |                |                       |              |

| 10                    | والمشتخب والمكرجي | DATA VALID OBH |                       |              |

| 11                    | WAIT              | WAIT           | NOT USED              |              |

| 12                    | NOT USED          | NOT USED       | <u>outpu</u> t enable |              |

| 13                    |                   | NOT USED       | RESET                 | NOT USED     |

| 14                    | IN OAH, DO        |                | IN 04H, D0            |              |

| 15                    | IN OAH, Dl        |                | IN 04H, Dl            | NOT USED     |

| 16                    | IN OAH, D2        |                |                       |              |

| 17                    |                   | IN OBH, D3     |                       |              |

| 18                    | IN OAH, D4        |                |                       | NOT USED     |

| 19                    | IN OAH, D5        | IN OBH, D5     | IN 04H, D5            | NOT USED     |

| . 20                  | IN OAH, D6        | IN OBH, D6     | IN 04H, D6            | DTR          |

| 21                    | IN OAH, D7        | IN OBH, D7     | IN 04H, D7            | DCD          |

| 22                    | +5 VDC            | +5 VDC         | NOT USED              | NOT USED     |

| 23                    |                   |                | INT                   | +TTY PRNTR   |

| 24                    | READ STB OAH      | READ STB OBH   | NOT USED              | -TTY KEYBD   |

| 25                    | GROUND            | GROUND         | GROUND                | -TTY PRNTR   |

|                       |                   |                |                       |              |

Connector Jl is dedicated to SCC parallel I/O port OAH, J2 to parallel I/O port OBH and J3 to parallel I/O port O4H. The SCC parallel output ports are discussed in Section 2.6. Connector J4 is dedicated to the SCC serial I/O port, and it is discussed in Section 2.7.

#### 2.6 SCC PARALLEL 1/0 PORTS

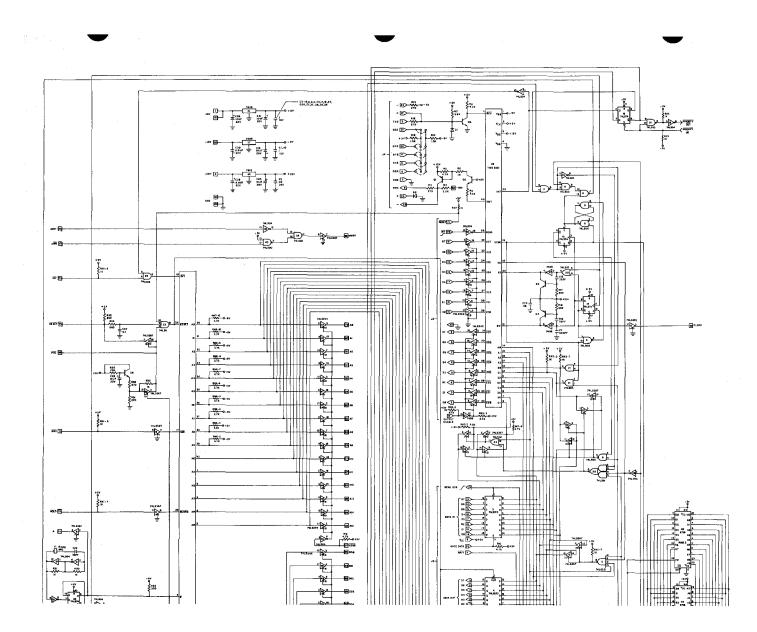

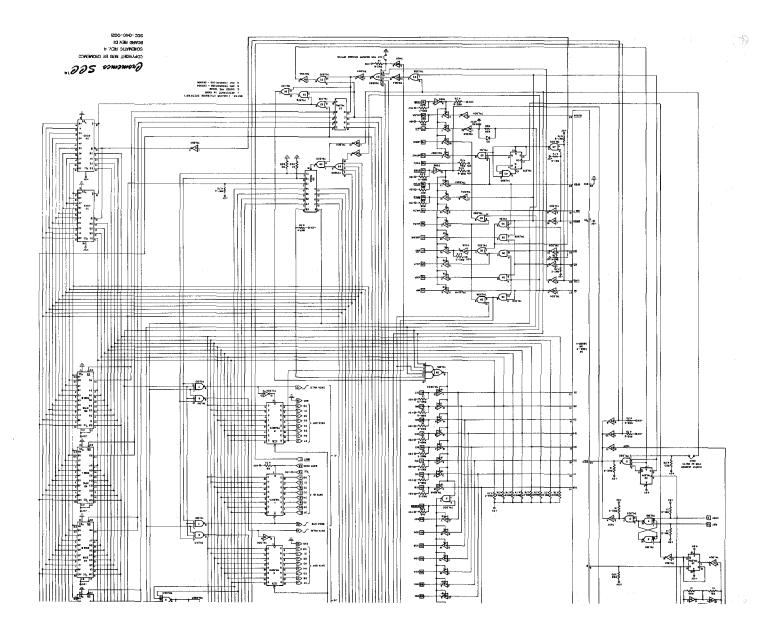

The SCC provides three parallel 8-bit output ports, and three parallel 8-bit input ports with fixed port addresses. Each of these six ports has its own dedicated uni-directional data lines (see SCC Schematic Diagram and Section 2.5). Two of these ports, IN 04H and OUT 04H, are an integral part of the 5501 Multi-Function I/O Controller (IC26), and the other four are implemented in either 74LS373 transparent octal latches (IN 0AH and IN 0BH), or 74LS273 octal latches with clear (OUT 0AH and OUT 0BH).

PARALLEL INPUT PORT 04H: A terminal device inputs parallel data to Z80A Register A thru port IN 04H by actively driving data lines D0 (LSB) thru D7 (MSB) on connector J3. These lines feed 74LS244 parts which represent 0.5 unit loads (logic 1) and 0.125 unit loads (logic 0), where a unit load is defined as a source current of 40 uAmps @ +2.4 VDC, and a sink current of 1.6 mAmps @ +0.4 The input data byte is not latched, but rather the Z80A must VDC. sample it in real time. The terminal device alerts the 280A that data is available by either an interrupt on S-100 line INT, or by a high-to-low transition on SCC line INT. This transition causes a bit to be set in the 5501's internal interrupt register. The 5501 may be programmed to prioritize and pass along the interrupt to the Z80A, or the Z80A may poll the 5501 for the interrupt source (see Section 2.9). The Z80A finally reads IN 04H data by executing an IN A,04H instruction, which loads the data byte into Register A, the Z80A accumulator. Note that bit D7 may be programmatically defined as auxiliary interrupt input PI7 (see

Section 2.9).

PARALLEL OUTPUT PORT 04H: Parallel data is transferred from the 280A to a terminal device via OUT 04H by first loading the data byte into Register A, then executing an OUT 04H, A instruction. Executing the output instruction causes the data byte to be routed, inverted and latched in the 5501's internal output register, which in turn presents the data to inverting 74LS240 tri-state drivers. The driver outputs feed SCC connector J3, and the drivers are brought out of the tri-state (floating) condition to actively drive D0 thru D7 in non-inverted form by asserting J3 line OUTPUT ENABLE active high. If OUTPUT ENABLE is left open, a pull-up resistor holds the line high thus permanently enabling active outputs. The 74LS240 drivers have a fan-out of 75 unit loads (logic 1) and 7.5 unit loads (logic 0). Note that an S-100 RESET does not clear port OUT 04H, nor does a POC. There are two other lines provided on connector J3; GROUND and RESET. Asserting RESET active low resets the 280A only; it does not connect to the S-100 bus line of the same name.

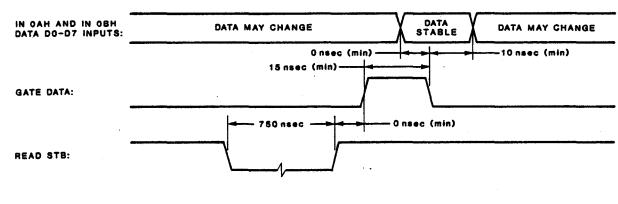

PARALLEL INPUT PORTS OAH & OBH: A terminal device inputs parallel data to the Z80A Register A thru ports IN OAH and IN OBH by actively driving data lines D0 thru D7 on either connector J1 (IN OAH) or J2 (IN OBH). Each set of lines feeds a 74LS373 transparent octal latch which represents 0.5 unit loads (logic 1) and 0.25 unit loads (logic 0). The input data byte may either be latched in the 74LS373 by a low-high-low transition on line GATE

DATA, or the 280A may sample the data in real time if GATE DATA is held high or left floating (then the latch outputs follow its inputs). If data is to be latched, a 0 nSec set-up time, and a 10 nSec data hold time is required relative to the high-to-low transition on GATE DATA. The 280A is alerted that new parallel input data is available again either thru S-100 bus line  $\overline{INT}$ , or thru J3 line  $\overline{INT}$ . The 280A reads the parallel input data by executing an IN A,0AH or an IN A,0BH, which loads the data by into 280A Register A. Status lines READ STB pulse low while the 280A is reading a 74LS373 latch, and its low-to-high transition is used by the terminal device to signal that the latch is ready for new data (see Figure 10).

LATCHING IN OAH AND IN OBH DATA

Figure 10: IN OAH AND IN OBH TIMING

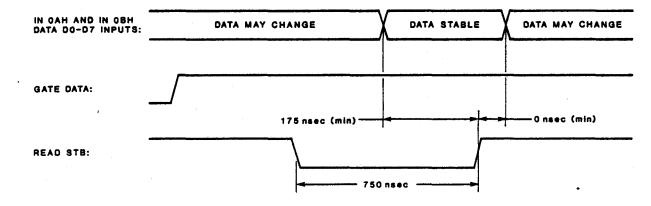

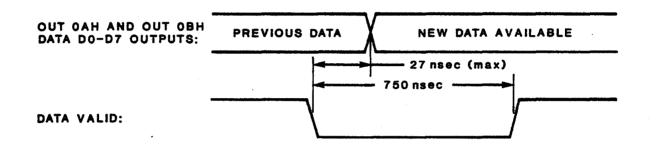

PARALLEL OUTPUT PORTS OAH & OBH: Parallel data is transferred to a terminal device thru port OUT OAH by first loading the data byte into Z80A Register A, then executing an OUT OAH, A instruction. Likewise, port OUT OBH is used by loading a data byte into Register A, then executing an OUT OBH, A instruction. Executing the output instruction routes the data byte to a 74LS273 octal latch, then causes the port's associated DATA VALID line to pulse low (see Figure 11). The low-to-high transition on DATA VALID signals the terminal device that valid parallel data is available at the 74LS273 outputs D0 thru D7. Each data line has a fan-out

of 20 unit loads (logic 1) and 10 unit loads (logic 0). An S-100 RESET or a POC clears both OUT OAH and OUT OBH. Note that bit D7 of OUT OAH controls SCC memory enable/disable if the MEMORY DISABLE option has been selected (see Section 2.4); otherwise D7 functions as an ordinary MSB data bit.

#### Figure 11: OUT OAH AND OUT OBH TIMING

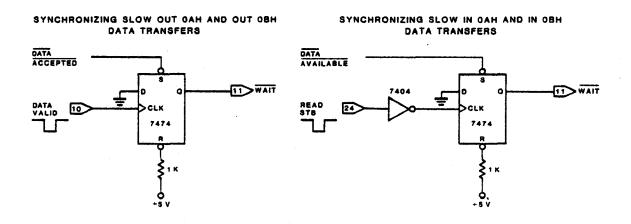

Connectors J1 and J2 also supply +5 VDC (pin 22), GROUND (pin 25), and a  $\overline{WAIT}$  line (pin 11) to external terminal devices. The  $\overline{WAIT}$  line may be used to insert wait states to synchronize the 280A to slow I/O devices. Example circuitry for this purpose is shown in Figure 12. To synchronize a slow output device connected to either OUT OAH or OUT OBH, the trailing edge of DATA VALID is used to force line  $\overline{WAIT}$  active low. The 280A then cycles in the wait state until user-defined line DATA ACCEPTED goes active low after the data has been read from the SCC output port, thus releasing the 280A to continue program execution.

To synchronize a slow input device connected to either IN OAH or IN OBH, the leading edge of READ STB is used to force line  $\overline{WAIT}$

active low. The Z80A then cycles in the wait state until userdefined line DATA AVAILABLE goes active low signaling that the input data has either stabilized (if sampling in real time), or has been latched by using the GATE DATA line. Line  $\overline{WAIT}$  then goes high which allows the Z80A to complete the input cycle, and continue normal program execution.

Figure 12: SYNCHRONIZING SLOW OUT OAH & OUT OBH I/O

#### 2.7 SCC SERIAL 1/0

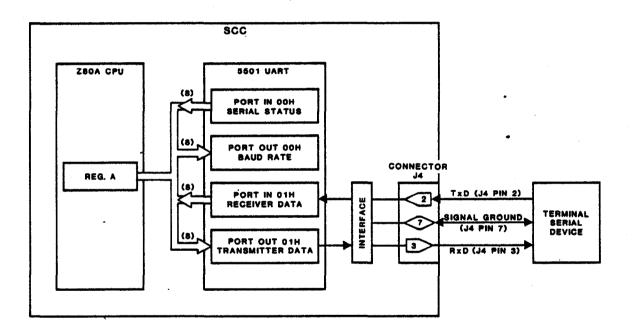

The primary serial data paths between the SCC and a serial terminal device are shown in Figure 13. Z80A Register A is the source register for data bytes transmitted to the terminal, and is also the destination register for data bytes received from the terminal. The 5501 Multifunction I/O Controller functions to convert parallel CPU data to serial terminal data, and vice versa, and additionally to supply serial status information and serial data control functions. TTL-level signals on the terminal side of the 5501 are converted to and from either RS-232 or 20 mA current

loop terminal data by SCC interface circuitry. Serial data to and from the terminal interfaces the SCC at connector J4. TRANSMITTER DATA from the SCC travels to an RS-232 terminal over line RxD, J4 pin 3, while RECEIVER DATA to the SCC travels from the terminal over line TxD, J4 pin 2 (RS-232 interface signals are labeled from the terminal's viewpoint).

#### Figure 13: SCC PRIMARY SERIAL DATA PATHS

Notice that even though a single 'serial terminal device' is used in the discussions and examples which follow, it is not the intention to exclude uni-directional serial devices such as printers, keyboards, and the like. The SCC serial input and

output channels may be managed independently with any mix of RS-232 and 20 mA current loop interfaces. The only practical restriction is a common serial transmit and receive baud rate.

The Z80A may determine status conditions <u>Read Data Available</u> (RDA) and <u>Transmitter Buffer Empty</u> (TBE) by periodically sampling SERIAL STATUS port IN 00H, or by programming the 5501 so that RDA and TBE conditions issue an interrupt request and their own RST instruction vectors to the Z80A (an interrupt-driven configuration), or by programming the 5501 so that RDA and TBE conditions issue a non-vectored interrupt request, followed by Z80A polling of INTERRUPT ADDRESS port IN 03H to determine the interrupt source (a polled-interrupt configuration). SCC interrupt behavior is topically covered in Sections 2.9 and 2.10, including serial I/O examples. The reader is referred to these sections for a thorough discussion of interrupt-related topics which are only touched upon in this section.

There are seven SCC I/O ports which may play a role in serial data exchanges; SERIAL STATUS (IN 00H), BAUD RATE (OUT 00H), RECEIVER DATA (IN 01H), TRANSMITTER DATA (OUT 01H), COMMAND REGISTER (OUT 02H), INTERRUPT ADDRESS (IN 03H) and INTERRUPT MASK (OUT 03H).

#### SERIAL STATUS, (IN 00H):

| ТВЕ | RDA | IPG | TBE | RDA | SRV | ORE | FME |

|-----|-----|-----|-----|-----|-----|-----|-----|

|-----|-----|-----|-----|-----|-----|-----|-----|

The Z80A interrogates this port by executing an IN A,(00H) instruction to determine the 5501 serial status. Individual bits of the status word are interpreted as follows:

BIT LABEL FUNCTION

- D7 TBE Transmitter Buffer Empty. The Transmitter Buffer is a temporary storage register which buffers the data byte sent to TRANSMITTER DATA (port OUT 01H). A logic 1 TBE indicates that the Transmitter Buffer is ready to accept a new data byte. TBE goes to logic immediately after the buffer contents are 1 transferred to the serial transmitter, thus the new data byte may be loaded into the buffer while transmission of the previous byte is still in progress. A TBE condition generates an interrupt request which may be either enabled or disabled by bit D5 of INTERRUPT MASK port OUT 03H (see Section 2.9). TBE is cleared to logic 0 when the Transmitter Buffer is loaded, and it is set to logic 1 after a 5501 RESET issued thru COMMAND REGISTER bit RES. THE status is also available at bit D4 (see below).

- RDA Read Data Available. A logic 1 RDA indicates that a data byte is available and may be read from RECEIVER DATA (port IN 01H). If a new data byte has arrived in its entirety before the previous contents of RECEIVER DATA have been read, the new byte will overwrite the old, and the OVERRUN error flag will be set to logic 1. An RDA condition generates an interrupt request which may be either enabled or disabled by bit D4 of INTERRUPT MASK port OUT 03H (see Section 2.9). The RDA flag is reset to logic 0 by either inputting RECEIVER DATA by executing an IN A,(01H) instruction, or by a 5501 RESET. RDA status is also available at bit D3 (see below).

D5

IPG

**D6**

Interrupt Pending. A logic l IPG indicates that one or more of the eight possible prioritized interrupt request sources is un-masked (enabled) and is currently requesting service. Bit IPG provides a means of sensing a service request from 5501 sources

when 280A interrupts are disabled. In this mode (I/O port-driven service), the 280A would read SERIAL STATUS port IN 00H under program control, test bit IPG, and if set to logic 1 (indicating an un-masked source is requesting service), INTERRUPT ADDRESS port IN 03H would then be read to identify the request source. EXAMPLE 5 below discusses a serial I/O programming example which uses IPG in this fashion.

- D4 TBE Transmitter Buffer Empty (identical to bit D7 described above).

- D3 RDA Read Data Available (identical to bit D6 described above).

- D2 SRV Serial Receive. A logic 1 SRV indicates a high level (marking) on the serial data input line, and a logic 0 SRV indicates a low level (spacing) on the serial data input line. SRV goes to logic 1 when no data is being received, and is provided for break detection and test purposes.

- Dl ORE Overrun Error. A logic 1 ORE indicates that a new RECEIVER DATA byte has overwritten a previous byte without the previous byte being read. ORE is reset to logic 0 after the SERIAL STATUS port is read, or by a 5501 RESET.

- D0 FME Frame Error. A logic 1 FME indicates an error in one or both stop bits which "framed" the last RECEIVER DATA byte. FME remains at logic 1 until a valid character is received.

#### BAUD RATE, (OUT 00H):

STOP 9600 4800 2400 1200 300 150 110 BITS

The Z80A sets the serial data transmit and receive baud rate, plus the number of stop bits, by outputting a control byte to this output port. The port is typically loaded as a system initialization task. A logic 0 output to bit D7 (STOP BITS) selects two stop bits, while a logic 1 to bit D7 selects one stop bit. A logic 1 in any bit position D6 thru D0 selects a baud

rate, with the correspondence tabulated below. If more than one of these bits is set to logic 1, the highest baud rate selected will result. If no bits D6 thru D0 are set to logic 1, the serial transmitter will be disabled. If COMMAND REGISTER bit D4 (High Baud, or HBD) is set to logic 1, the baud rate will undergo an eightfold increase. The bit assignments follow:

| BIT                                    | FUN                                                                                      | CTION                                                                                           |

|----------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| D7                                     | STOP BITS                                                                                |                                                                                                 |

| D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0 | 9,600 BAUD<br>4,800 BAUD<br>2,400 BAUD<br>1,200 BAUD<br>300 BAUD<br>150 BAUD<br>110 BAUD | 76,800 BAUD<br>38,400 BAUD<br>19,200 BAUD<br>9,600 BAUD<br>2,400 BAUD<br>1,200 BAUD<br>880 BAUD |

|                                        | (HBD = LOGIC 0)                                                                          | (HBD = LOGIC 1)                                                                                 |

RECEIVER DATA, (IN 01H):

|   | DATA | BYTE | FROM   | TERMI | NAL |  |

|---|------|------|--------|-------|-----|--|

| 1 | 1    | (    | SHIFT) | . 1   |     |  |

The Z80A reads an assembled data byte from the serial terminal device by reading this port. The Z80A is alerted that data is available either by testing SERIAL STATUS bit IPG and then polling INTERRUPT ADDRESS port IN 03H for the encoded RDA address, or by directly sampling SERIAL STATUS bit RDA. Note that status bit RDA is always valid, even if RDA has been masked-off as an interrupt source thru INTERRUPT MASK port OUT 03H.

TRANSMITTER DATA, (OUT 01H):

| I        |  |  |  | 1 | <u> </u> |   |

|----------|--|--|--|---|----------|---|

| CHIFT)   |  |  |  |   |          |   |

| (Graf 1) |  |  |  |   |          |   |

|          |  |  |  |   |          | 1 |

The Z80A writes to this output port to send data to the serial terminal device. The Z80A is alerted that the Transmitter Buffer is empty either by testing SERIAL STATUS bit IPG and then polling INTERRUPT ADDRESS port IN 03H for the encoded TBE address, or by directly sampling SERIAL STATUS bit TBE. Note that status TBE is always valid, even if TBE has been masked-off as an interrupt source thru INTERRUPT MASK port OUT 03H.

COMMAND REGISTER, (OUT 02H):

NOT. NOT HBD INE BRK RES r/\$7 **785** USED USED

The Z80A configures the 5501 by loading this output port. Three COMMAND REGISTER bits may have an effect on SCC serial I/O operations; HBD, INE, BRK and RES.

BIT LABEL FUNCTION

- D4 HBD High Baud. Setting HBD to logic 1 octuples the 5501 internal clock frequency, causing the serial transmit and receive baud rate to octuple.

- D3 INE INTA Enable. The 5501 monitors the data bus at SYNC of each machine cycle to determine if the Z80A is entering an Interrupt Acknowledge (INTA) cycle. Resetting INE to logic 0 causes the 5501 to ignore all INTA cycles. Setting INE to logic 1 causes the TMS 5501 to accept an INTA, and gate one-of-eight RST instructions onto the data bus to service the interrupt. See Sections 2.9 and 2.10 for discussions on interrupt servicing RDA and TBE requests.

33

- DI BRK Break. Setting BRK to logic l latches the serial transmitter output XMT in the low (spacing) state. Resetting BRK to logic 0 allows the serial transmitter to operate normally. RES overrides BRK.

- DO RES 5501 Reset. Setting RES to logic 1 results in the following:

(1) SERIAL STATUS bits RDA, SBD, FBD and ORE are reset to logic 0; the serial receiver goes into the 'search for new character' mode; the current contents of RECEIVER DATA, port IN 01H, is not affected and contains the last character received.

(2) SERIAL STATUS bit TBE is set to logic 1; the serial transmitter output XMT goes high (marking). RES overrides BRK if both are set to logic 1 in the same command byte.

(3) RES is automatically reset to logic 0 after the steps listed above (and some other reset operations described in Section 2.9) are completed. The 5501 is then ready for 'normal' serial I/O operations.

INTERRUPT ADDRESS. (IN 03H):

Lg L1 Lo 1

This port is provided for identifying 5501 service request sources by polling. If interrupts are disabled, the Z80A may still sense an interrupt pending condition by testing SERIAL STATUS bit IPG, and then read INTERRUPT ADDRESS to determine the interrupt source. Interrupt sources TBE and RDA, along with six others, may be determined by reading and properly interpreting the contents of this port. Reading INTERRUPT ADDRESS contents 0E7H implies an RDA condition; reading an 0EFH implies a TBE condition. An RDA request has priority over a TBE request if both are simultaneously active. For full details on all eight interrupt sources and their priorities, see Section 2.9.

INTERRUPT MASK, (OUT 03H):

TIMER 5 OR TIMER TIMER TIMERITIME RDA TBE

Individual bits output to this port selectively enable or inhibit the eight 5501 sources from issuing an interrupt request to the Z80A, and from being prioritized and encoded in the INTERRUPT ADDRESS register. Setting INTERRUPT MASK bit D5 to logic 1 enables interrupt source TBE as described above; resetting bit D5 to logic 0 inhibits it. Likewise, bit D4 controls interrupt source RDA. Note again that SERIAL STATUS bits RDA and TBE are always valid, regardless of the control bits D4 and D5 output to the INTERRUPT MASK port.

Three serial I/O example programs will now be presented. The program segments which follow are assumed resident in 2716 socket ROM 0 (0000H - 07FFH). The first example deals with initializing an SCC system connected to a serial terminal.

#### EXAMPLE 3

This example assumes an SCC system utilizing SCC on-board memory only, and an RS-232 CRT terminal attached to SCC serial connector J4. An S-100 bus RESET or a POC automatically starts program execution at address 0000H, so the routine begins there by moving the stack out to the end of SCC read/write memory, then by forcing a jump to the 5501 initialization routine starting at address 100H. The main initialization code is located at 100H so as to leave low memory free for RST 08H thru RST 38H service routines. Notice that the RST 00H service area is occupied by the first two instructions below. The 5501 is initialized by loading three registers: BAUD RATE (OUT 00H); COMMAND REGISTER (OUT 02H); and INTERRUPT MASK (OUT 03H). This routine configures the SCC to transfer serial data exclusively thru reading and loading I/O ports, not by responding to interrupt requests. Note that an S-

100 bus RESET or POC automatically disables interrupts, thus the 280A will simply ignore any active low request on its INT input pin. The SCC system is configured as follows:

(1) The serial data baud rate is set to 9600, one stop bit.

(2) The 5501 internal clock is set to low baud (HBD = logic 0).

(3) The 5501 is programmed to ignore INTA cycles. This is for emphasis only, since interrupts are disabled and the Z80A will not enter an INTA cycle.

(4) Bit D7 of port OUT OAH is used as an ordinary data bit, not as auxiliary interrupt source PI7.

(5) The 5501 is reset.

(6) All 5501 interrupt sources are un-masked, so that they may be polled thru INTERRUPT ADDRESS port IN 03H (see EXAMPLE 5 below).

# CROMEMCO CDOS 280 ASSEMBLER version 02.15

|      |        | 0001 ;<br>0002 ; >><br>0003 ;<br>0004 ;<br>0005 ; | > INI  | TIALIZE SCC | 5501 | ROUTINE | <<<                |

|------|--------|---------------------------------------------------|--------|-------------|------|---------|--------------------|

|      | (0000) | 0006 BAUD:                                        | EQU    | 00H         |      | ;BAUD   | RATE PORT          |

|      | (0002) | 0007 COMREG                                       | EQU    | 02H         |      | ; COMM  | AND REG. PORT      |

|      | (0003) | 0008 INTMSK                                       | EQU    | 03H         |      |         | RRUPT MASK PORT    |

|      | (23FF) | 0009 ENDRAM                                       | EQU:   | 23FFH       |      | ;SCC    | END RAM ADDR.      |

|      |        | 0010                                              |        | _           |      | 7       |                    |

|      |        | 0011                                              | ORG    | 0           | •    | ,SCC    | POC OR RESET       |

|      |        | 0012                                              |        |             |      | ;       |                    |

| 0000 | 31FF23 | 0013                                              | LD     | SP, ENDRAM  |      | •       | K TO ENDRAM        |

| 0003 | C30001 | 0014                                              | JP     | IN5501      |      | ;JUMP   | TO INIT.           |

|      |        | 0015                                              |        |             |      | 7       |                    |

|      |        | 0016<br>0017 ; INI                                |        | E 5501      |      | ;       |                    |

|      |        | 0017 ; INT.                                       | LINDIA | E 2201      |      | •       |                    |

|      |        | 0019                                              | ORG    | 100H        |      | • POUT  | INE START          |

|      |        | 0020                                              | OV0    | 1001        |      | ,       |                    |

| 0100 | F3     | 0021 IN5501                                       | DI     |             |      | : (EMP  | HASIS ONLY)        |

| 0101 | 3E01   | 0022                                              | LD     | A,00000011  | в    |         | AND BYTE           |

| 0103 | D302   | 0023                                              | OUT    | COMREG, A   |      |         | OMMAND REG.        |

| 0105 | 3EC0   | 0024                                              | LD     | A,11000000  | В    | ;BAUD   | STOP BIT BYTE      |

| 0107 | D300   | 0025                                              | OUT    | BAUD, A     |      | TO B    | AUD RATE REG.      |

| 0109 | 3EFF   | 0026                                              | LD     | A,11111111  | В    |         | RRUPT MASK         |

| 010B | D303   | 0027                                              | OUT    | INTMSK, A   |      |         | ASK ALL SOURCES    |

| 010D | C30002 | 0028                                              | JP     | COMLIN      |      | ;CONT   | INUED NEXT EXAMPLE |

| 0110 | (0100) | 0029                                              | END    | IN5501      |      |         |                    |

|      |        |                                                   |        |             |      |         |                    |

The next programming example illustrates serial I/O managed

by SERIAL STATUS bits RDA and TBE.

# EXAMPLE 4

Continuing the example above, assume that after system initialization, the SCC system awaits a 'command line', which the user enters from the CRT keyboard, to determine further actions. The program segment below then receives a serial data byte from the terminal, echoes it back, stores it sequentially in a read data buffer with previously received bytes starting at RAM location RDBUFF, and then awaits another data byte. Character Carriage Return <CR> is defined to be the command line delimiter, and it is echoed to the terminal as CR-LF (Carriage Return followed by a Line Feed). After a CR character is stored in the read buffer, program execution continues by jumping to an undefined 'command line interpretation' program segment, with an assumed starting address of COMITP. Notice that RDA and TBE conditions are determined by sampling the SERIAL STATUS port, and that an overrun error, a framing error, or a command line in excess of 72 characters resets the RAM read buffer and causes the message 'RE-ENTER LINE' to be sent to the terminal.

CROMEMCO CDOS Z80 ASSEMBLER version 02.15

|                                                                    | 0001 ;<br>0002 ; >>><br>0003 ;<br>0004 ;                                                             | COMMAND LINE INPUT R                                                                                                  | OUTINE <<<                                                                                                                                                            |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (0300)<br>(000D)<br>(0003)<br>(000A)<br>(0048)                     | 0005 COMITP:<br>0006 CR:<br>0007 ERRMSK:<br>0008 LF:<br>0009 MAXLEN:                                 | EQU 300H<br>EQU 0DH<br>EQU 00000011B<br>EQU 0AH<br>EQU 72                                                             | ;ARBITRARY ROM 0 ADDR<br>;ASCII 'CR'<br>;ORE & FME MASK<br>;ASCII 'LF'<br>;MAX LINE LENGTH                                                                            |

| (007F)<br>(0006)<br>(0001)<br>(2000)<br>(0000)<br>(0007)<br>(0001) | 0010 MSBMSK:<br>0011 RDA:<br>0012 RDATA:<br>0013 RDBUFF:<br>0014 STATUS:<br>0015 TBE:<br>0016 TDATA: | EQU 0111111B<br>EQU 6                                                                                                 | ;D7 (MSB) MASK<br>;RDA BIT D6<br>;RECEIVER DATA PORT<br>;START READ BUFF<br>;SERIAL STATUS PORT<br>;TBE BIT D7<br>;XMITTER DATA PORT                                  |

| 23.0020                                                            | 0017<br>0018<br>0019                                                                                 | ORG 200H                                                                                                              | ;<br>COMLIN START ADDR<br>;IN SCC ROM 0                                                                                                                               |

| 210020<br>0E48<br>DB00<br>CB77<br>28FA<br>E603<br>201C<br>0D       | 0020 COMLIN:<br>0021<br>0022 TSTRDA:<br>0023<br>0024<br>0025<br>0026<br>0027                         | LD HL, RDBUFF<br>LD C, MAXLEN<br>IN A, STATUS<br>BIT RDA, A<br>JR Z, TSTRDA<br>AND A, ERRMSK<br>JR NZ, ERROR<br>DEC C | ; POINT TO READ BUFF<br>; MAX LINE LENGTH<br>; READ SERIAL STATUS<br>; RDA?<br>; RE-CHECK RDA IF NO<br>; RDA. ORE OR FME?<br>; OUT MESSAGE IF SO<br>; DECR BYTE COUNT |

.

| 0210         | 2819     | 0028        | JR              | Z, ERROR           | ;OUT MESSAGE IF ZERO                    |

|--------------|----------|-------------|-----------------|--------------------|-----------------------------------------|

| 0212         | DB01     | 0029        | IN              | A, RDATA           | ; ELSE READ BYTE                        |

| 0214         | E67F     | 0030        | AND             | MSBMSK             | MASK-OFF MSB                            |

| 0216         | 77       | 0031        | LD              | (HL),A             | CHAR TO BUFFER                          |

| 0217         | 47       | 0032        | LD              | B,A                | AND TO REG. B                           |

| 0218         | CD4B02   | 0033        |                 | OUTCHR             | ECHO CHARACTER                          |

| 021B         | 3EOD     | 0034        | LD              | A,CR               | ;WAS IT A 'CR'?                         |

| 021D         | B8       | 0035        | CP              | B                  |                                         |

| 021E         | 2803     | 0036        | JR              | Z . COMEND         | COM LINE END IF SO                      |

| 0220         | 2303     | 0038        | INC             | HL                 |                                         |

| 0221         | 18E2     | 0038        |                 |                    | ; MOVE BUFFER POINTER                   |

| 0221         | TOFT     | 0039        | JR              | TSTRDA             | BACK FOR NEXT CHAR                      |

| 0000         | 0000     |             |                 |                    |                                         |

| 0223         | 060A     | 0040 COMEND | •               | B,LF               | ;ASCII 'LF' TO REG. B                   |

| 0225         | CD4B02   | 0041        |                 | OUTCHR             | ;'LF' TO TERMINAL                       |

| 0228         | C30003   | 0042        | JP              | COMITP             | COMLIN ROUTINE EXIT                     |

|              |          | 0043        |                 |                    | ;                                       |

| 022B         | 213A02   | 0044 ERROR: |                 | hl, Mesbeg         | ; POINT MESSAGE BEGIN                   |

| 022E         | 0E11     | 0045        | LD              | C, MESEND-MESBEG   | ; MESSAGE BYTE COUNT                    |

| 0230         | 46       | 0046 NXTCHR |                 | B,(HL)             | ; CHAR TO REG. B                        |

| 0231         | CD4B02   | 0047        | CALL            | OUTCHR             | ; CHAR TO TERMINAL                      |

| 0234         | 0D       | 0048        | DEC             | С                  | ;DECR BYTE COUNT                        |

| 0235         | 28C9     | 0049        | JR              | 2, COMLIN          | RESTART COMLIN IF 0                     |

| 0237         | 23       | 0050        | INC             | HL                 | ELSE MOVE POINTER                       |

| 0238         | 18F6     | 0051        | JR              | NXTCHR             | OUT NEXT MESS. CHR                      |

|              |          | 0052        |                 |                    | ;                                       |

| 023A         | ODOA     | 0053 MESBEG | : DB            | CR, LF             | BEGIN MESSAGE                           |

| 023C         | 52452D45 | 0054        | DB              | 'RE-ENTER LINE'    | ; ;                                     |

|              | 4E544552 |             |                 |                    | •                                       |

|              | 204C494E |             |                 |                    |                                         |

|              | 45       |             |                 |                    |                                         |

| 0249         | ODOA     | 0055        | DB              | CR, LF             | ;END MESSAGE                            |

|              | (024B)   | 0056 MESEND | : EOU           | Ś                  | <b>1</b>                                |

|              | (        | 0057        |                 | •                  | 3                                       |

|              |          | 0058 ;      |                 |                    | •                                       |

|              |          | 0059 ; >>>  | SUBB            | OUTINE OUTCHR <<<  |                                         |

|              |          | 0060 ;      | 0001            |                    |                                         |

|              |          |             | τ. <b>WT</b> ΨH | ASCII CHARACTER I  | N REC B                                 |

|              |          |             |                 | ITH REG. A & FLAGS |                                         |

|              |          | 0063 ;      | OTTO N          | III KUG. A S PDAGO | CHANGED.                                |

| 024B         | DB00     | 0064 OUTCHR |                 | A, STATUS          | READ SERIAL STATUS                      |

| 024D         | CB7F     |             |                 | •                  | • • • • • • • • • • • • • • • • • • • • |

| 024D<br>024F | 28FA     | 0065        | BIT             | TBE, A             | TBE?                                    |

|              |          | 0066        | JR              | Z, OUTCHR          | LOOP BACK IF NOT                        |

| 0251         | 78       | 0067        | LD              | A,B                | TBE. GET CHARACTER                      |

| 0252         | D301     | 0068        | OUT             | TDATA, A           | CHAR TO TERMINAL                        |

| 0254         | C9       | 0069        | RET             |                    | ; RETURN                                |

| 0055         | (0000)   | 0070        | -               | 20WI 11            | ;                                       |

| 0255         | (0200)   | 0071        | END             | COMLIN             |                                         |

|              |          |             |                 |                    |                                         |

The next example illustrates how INTERRUPT ADDRESS port IN

------

03H may be used for serial data exchange in an I/O port-driven (Z80A interrupts disabled) environment. Note that when interrupts are disabled (by a RESET, a POC or executing a DI instruction), and when one or more 5501 interrupt sources are un-masked (enabled), then an interrupt request from one of these sources will force Z80A pin INT low, but the Z80A will ignore the request since interrupts are disabled. The Z80A discovers that an interrupt is pending by sampling SERIAL STATUS bit IPG, and may then read the highest priority enabled interrupt source requesting service by reading INTERRUPT ADDRESS port IN 03H.

#### EXAMPLE 5

The following program segment assumes the SCC system has been initialized as per EXAMPLE 3 prior to execution. The routine initiates a 10 mSec timing interval using TIMER 4, and at the end of the interval outputs a period character to the terminal. This process is repeated indefinitely until any terminal key is pressed, which causes a branch to address EXIT (to an undefined program segment). Note that all interrupt sources other than RDA and TIMER 4 are masked-off (disabled). If an RDA condition occurs, IPG is set to logic 1, and the contents of INTERRUPT ADDRESS port IN 03H becomes 0E7H. When TIMER 4 reaches DELAY COUNT zero (one count per 64 uSec), IPG is set to logic 1, and the INTERRUPT ADDRESS becomes 0F7H. The INTERRUPT ADDRESS contents will be 0E7H if RDA and TIMER 4 are both active, since RDA has higher priority than TIMER 4.

CROMEMCO CDOS Z80 ASSEMBLER version 02.15

|              |              | 0001 ;<br>0002 ;<br>0003 ;<br>0004 ;<br>0005 ; | >>>   | 1/0          | PORT POLLING <<  | <     |                                       |

|--------------|--------------|------------------------------------------------|-------|--------------|------------------|-------|---------------------------------------|

|              | (0500)       | 0006 EX                                        | IT:   | EQU          | 500H             | : A F | BITRARY ROM 0 ADDR.                   |

|              | (0003)       |                                                |       | EQU          | 03H              |       | TERRUPT ADDR. PORT                    |

|              | (0003)       | 0008 IN:                                       |       |              | 03H              | •     | TERRUPT MASK PORT                     |

|              | (0005)       | 0009 IPC                                       | G :   | EQU          | 05H              | ; IN  | T. PENDING BIT D5                     |

|              | (0000)       | 0010 ST2                                       | ATUS: | EQU          | 00H              |       | RIAL STATUS PORT                      |

|              | (0001)       | 0011 TD/                                       | ATA:  | EQU          | 01H              | ; XM  | ITTER DATA PORT                       |

|              | (009C)       | 0012 TEN                                       |       | EQU          | 9CH              | ;10   | MSEC TIMER COUNT                      |

|              | (0008)       | 0013 TIN                                       | MER4: | EQU          | 08H              | ;TI   | MER 4 PORT                            |

|              |              | 0014                                           |       |              |                  | ;     |                                       |

| 0000'        |              | 0015                                           |       | ORG          | 400H             | ; RC  | OUTINE START                          |

|              |              | 0016                                           |       |              |                  | ;     |                                       |

| 0400         | 3E50         | 0017 IO                                        |       |              | A,01010000B      | •     | TERRUPT MASK ALL                      |

| 0402         | D303         | 0018                                           |       | OUT          | INTMSK, A        |       | T RDA & TIMER 4                       |

| 0404         | 3E9C         | 0019 CYC                                       |       |              | A, TENMS         | •     | T TIMER COUNT                         |

| 0406         | D308 ·       | 0020                                           |       | OUT          | TIMER4,A         |       | ART TIMER 4                           |

| 0408         | DB00         | 0021 CHP                                       |       |              | A, STATUS        |       | T SERIAL STATUS                       |

| 040A         | CB6F         | 0022                                           |       | BIT          | IPG,A            | ;IP   |                                       |

| 040C<br>040E | 28FA         | 0023                                           |       | JR           | Z, CHKIPG        | •     | -CHECK IF NO                          |

| 0402         | DB03<br>FEE7 | 0024<br>0025                                   |       |              | A, INTADR        | ;YE   |                                       |

| 0410         | CA0005       | 0025                                           |       |              | 0E7H             | ; RD  |                                       |

| 0415         | 3E2E         | 0020                                           |       |              | Z,EXIT           | •     | S, EXIT.                              |

| 0417         | D301         | 0028                                           |       |              | A,'.'<br>TDATA,A |       | , MUST BE TIMER 4<br>RIOD TO TERMINAL |

| 0419         | 18E9         | 0029                                           |       |              | CYCLE            |       | CK, RE-LOAD TIMER                     |

| 041B         | (0400)       | 0030                                           |       | END          | IOPOLL           | j DA  | CA, RE-DOAD TIMER                     |

| V-110        | (0400)       |                                                |       | 911 <b>9</b> |                  |       |                                       |

The serial I/O programs discussed thus far have been written in Z80 assembly language. If programming in Cromemco's 3K Control Basic, then all serial I/O may be left to the management of the interpreter. Alternately, a 3K Control Basic program can manage 'non-standard' serial I/O thru its IN (I/O port read) function and its OUT (I/O port write) and CALL (assembly language subroutine) instructions, provided their use is consistent with the serial I/O specifications and descriptions given above.

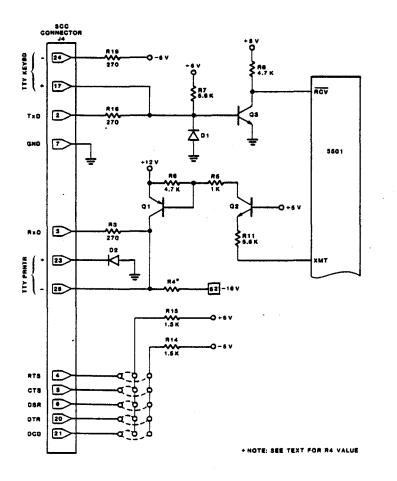

A schematic of the RS-232 / 20 mA current loop serial

.40

interface appears in Figure 14. A 20 mA current loop interface involves four lines: TTY KEYBD (+); TTY KEYBD (-); TTY PRNTR (+); and TTY PRNTR (-). An RS-232 interface would typically involve at least signal lines TxD, RxD and GND, and may optionally define Modem Control lines RTS (Request to Send), CTS (Clear to Send), DSR (Data Set Ready), DTR (Data Terminal Ready) and DCD (Data Carrier Detect).

Figure 14: SCC SERIAL INTERFACE

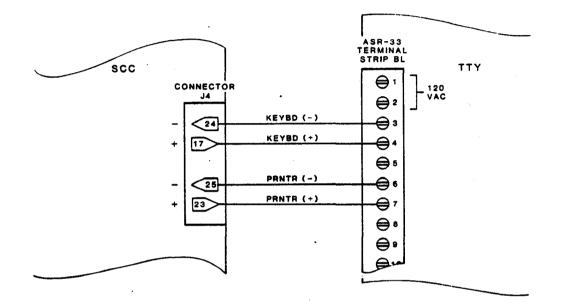

An ASR-33 TTY interface is illustrated in Figure 15. If the SCC 20 mA current loop interface is used, SCC resistor R4 must be

replaced with an 850 ohm, 1 watt resistor. If the current loop interface is not used, leave the factory installed 3.3 Kohm, 1/4 watt resistor R4 in place to reduce power consumption and heat. Caution: 120 VAC is present on ASR-33 terminal strip 'BL'.

Figure 15: ASR-33 TO SCC INTERFACE

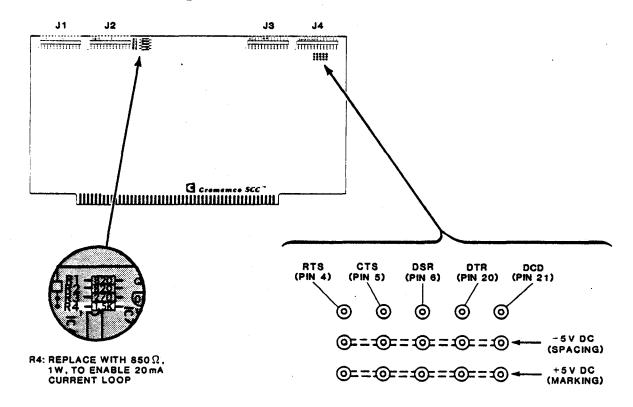

When using the SCC RS-232 interface, Modem Control lines RTS, CTS, DSR, DTR and DCD may either be left floating (factory shipped condition), or they may be selectively defined high (marking) or low (spacing) by installing insulated jumper wires between selected soldering pads as illustrated in Figure 17. The RS-232 high (spacing) level output by the SCC is +5 VDC, and the low (marking) level is -5 VDC; the SCC will accept any input levels which meet RS-232 specifications. Note that Cromemco supplied interface cables are terminated in an EIA DB-25S female connector, and the pin-outs of these cables meet RS-232 pin definitions except for pins 17 (+TTY KEYBD), 23 (+TTY PRNTR), 24 (-TTY KEYBD)

and 25 (-TTY PRNTR). Exercise caution when connecting this cable to devices which may make different use of these lines.

Figure 16: SCC MODEM CONTROL JUMPER PADS

#### 2.8 SCC INTERVAL TIMERS

The SCC provides five independent interval timers, referred to explicitly as TIMER 1 thru TIMER 5 in this manual (the five timers are an integral part of the 5501 Multifunction I/O Controller). The SCC timers are selectively enabled for use, or disabled, by bits of INTERRUPT MASK port OUT 03H (see below). This is usually done as part of the system initialization routine. Setting an INTERRUPT MASK to logic 1 enables its associated timer, resetting a bit disables it.

#### INTERRUPT MASK BITS (OUT 03H)

(LOGIC 1 = ENABLE; LOGIC 0 = DISABLE) BIT FUNCTION

| סס | TIMER 5 OR PI7         |

|----|------------------------|

| D6 | TIMER 4                |

| D5 | TBE                    |

| D4 | RDA                    |

| D3 | TIMER 3                |

| D2 | <b>INT (J4 PIN 23)</b> |

| Dl | TIMER 2                |

| D0 | TIMER 1                |

Another initialization task is choosing between TIMER 5 and auxiliary interrupt input PI7 (MSB bit D7 of port IN 04H) as a possible interrupt source. PI7 is selected by setting COMMAND REGISTER bit RS7 to logic 1, while resetting RS7 to logic 0 selects TIMER 5.

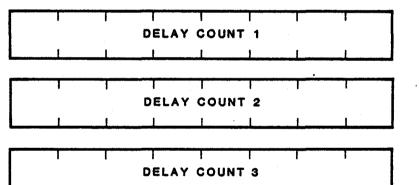

Each timer is assigned an SCC output port (see below), which may be loaded with a one-byte DELAY COUNT (00H - 0FFH, or 0 thru 255 decimal). After initial loading, the DELAY COUNT is decremented once every 64 uSec if COMMAND REGISTER bit HBD = logic 0, or once every 8 uSec if HBD = logic 1. The maximum delay from initial loading to timeout (DELAY COUNT zero) is then 16.32 mSec, and the accuracy from loading to timeout is plus 0 uSec and minus 64 uSec (or minus 8 uSec if HBD = logic 1).

# SCC TIMER PORT ASSIGNMENTS

| TIMER | 1 | OUT | 0 5 H |

|-------|---|-----|-------|

| TIMER | 2 | OUT | 06H   |

| TIMER | 3 | OUT | 07H   |

| TIMER | 4 | OUT | 08H   |

| TIMER | 5 | OUT | 09H   |

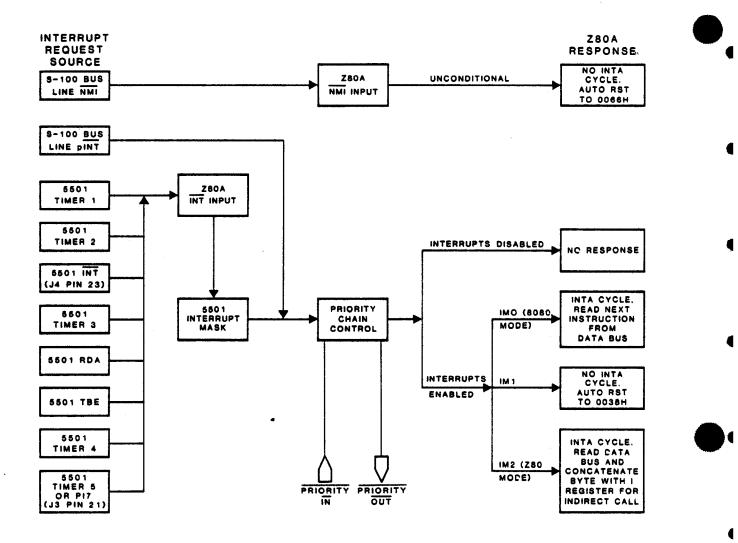

The Z80A is alerted that an enabled (un-masked) timer has reached DELAY COUNT zero in one of three ways:

(1) If interrupts are disabled, the Z80A finds SERIAL STATUS bit IPG set to logic 1. INTERRUPT ADDRESS port IN 03H is then read to identify the interrupt request source. Reading the INTERRUPT ADDRESS contents causes IPG to be reset to logic 0 if no other interrupt requests are pending. Notice that this method involves only reading SCC input ports SERIAL STATUS and INTERRUPT ADDRESS; the Z80A ignores its own INT input pin, and does not enter an INTA cycle.

(2) If interrupts are enabled (by executing an EI instruction) and COMMAND REGISTER bit INE (INTA Enable) is set to logic 1, and the timer in question is enabled, then a timeout interrupts the Z80A, and automatically gates an RST instruction onto the data bus in response to the Z80A-issued INTA cycle (an interrupt-driven configuration). Each timer is assigned its own unique RST instruction.

(3) If interrupts are enabled, and COMMAND REGISTER bit INE is reset to logic 0, and the timer in question is enabled, then a timeout interrupts the Z80A, and the interrupt service routine would then read INTERRUPT ADDRESS port IN 03H to identify the interrupt request source (a polled-interrupt configuration).

The above description applies to an enabled timer. A timer disabled by a logic 0 INTERRUPT MASK bit may be loaded with a DELAY COUNT, it will count down to timeout and generate an interrupt request, but the interrupt request will not pass thru the INTERRUPT MASK, will not set bit IPG to logic 1, and will not place an encoded address in INTERRUPT ADDRESS. A detailed discussion of timer service modes (2) and (3) above appears in Section 2.9, and programming examples appear in Section 2.10. The

remainder of this section assumes the timer service mode (1) above.

Again, if an enabled timer reaches timeout, bit IPG is set to logic 1. Loading a DELAY COUNT of 00H causes an immediate interrupt request, and loading a new DELAY COUNT before timeout re-initializes the timer without generating an interrupt request. After reading bit IPG set to logic 1, the Z80A reads the INTERRUPT ADDRESS port to identify the interrupt request source, and interprets its contents as follows:

#### INTERRUPT ADDRESS (IN 03H)

| CONTENTS | INTERRUPT SOURCE | PRIORITY |

|----------|------------------|----------|

| 0C7H     | TIMER 1          | HIGHEST  |

| OCFH     | TIMER 2          |          |

| 0D7H     | INT (J4 PIN 23)  |          |

| ODFH     | TIMER 3          | •        |

| 0E7H     | RDA              |          |

| 0 EFH    | TBE              |          |

| OF7H     | TIMER 4          |          |

| OFFH     | TIMER 5 OR PI7   | LOWEST   |

|          | OR NO INT REQ    |          |

The contents of INTERRUPT ADDRESS always points to the highest priority enabled interrupt source currently requesting service. In particular, if a higher priority interrupt request occurs after a lower priority request, the contents of INTERRUPT ADDRESS will change to reflect the higher priority request, and the lower priority request will be 'pushed down' one position in the queue. The interrupt sources are prioritized as shown above, with TIMER 1 assigned the highest priority, and TIMER 5/P17 the lowest.

The following programming example illustrates SCC timer initialization, simultaneous control of two independently maintained timers, generating timing intervals in excess of 16.32 mSec, and use of interrupt source PI7.

# EXAMPLE 6

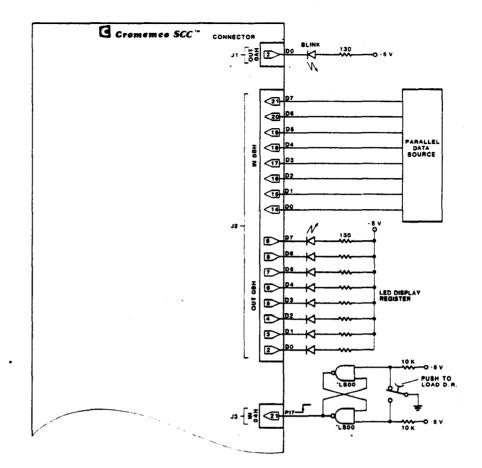

Suppose an SCC system is to monitor a parallel input device connected to port IN 0BH by reading it approximately once every 3 mSec. Further assume it is of interest to know how often the sampled data byte exceeds 0F0H in value. The program segment below uses TIMER 1 to generate the 3 mSec intervals, and maintains a tally of 'overcount' samples in Z80A Register C. For simplicity, it is assumed that overflowing Register C is not possible. The program also maintains TIMER 2 for the purpose of blinking an LED indicator ON and OFF once every two seconds to evidence ongoing program execution. The blinking indicator is assumed connected to bit D0 of port OUT 0AH (see Figure 17). Further, the program defines PI7 as an interrupt source by setting COMMAND REGISTER bit RS7 to logic 1. A low-to-high transition on PI7 (D7 of port IN 04H) causes the program to output the contents of Register C to an 8-bit LED display register connected to port OUT 0BH, to clear Register C, and then to resume port IN 0BH sampling as described above.

Figure 17: EXAMPLE 6 SCC CONFIGURATION

CROMEMCO CDOS Z80 ASSEMBLER version 02.15

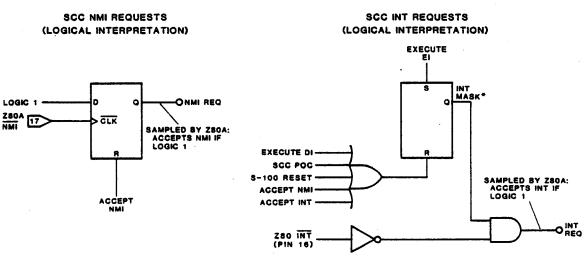

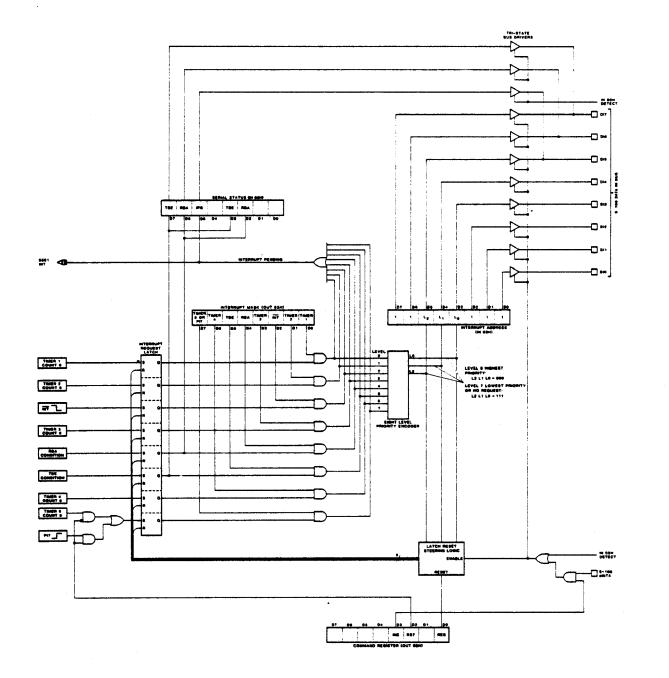

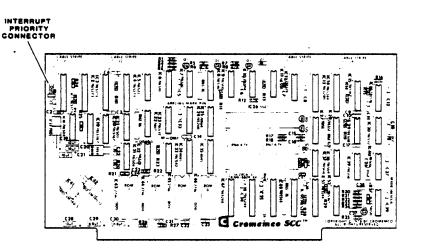

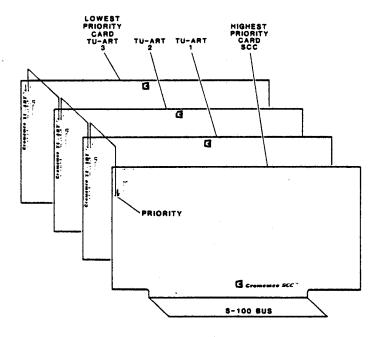

|        | 0001 ;<br>0002 ; >>><br>0003 ;<br>0004 ; | SCC TIMER | EXAMPLE ROUTINE <<<   |